文章图片

文章图片

文章图片

文章图片

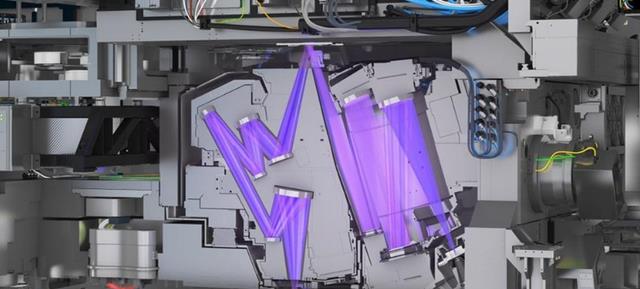

EUV光刻机在芯片制造产业被视作天花板的存在 , 最先进的技术 , 最多的零部件以及耗费生产资源最大的EUV光刻机 , 一台价值1.2亿美元 , 而且是有钱也买不到的那种 。 ASML凭借EUV光刻机的生产出货 , 成为全球最大的光刻机制造商 。

可就是这种被视作神话 , 天花板的EUV光刻机却凸显出了“隐疾” , ASML不愿看到的情况正在发生 。 这是什么情况?ASML , 芯片制造商们该如何应对?

EUV光刻机的“隐疾”全球芯片制造商几乎都在抢购ASML生产的EUV光刻机 , 以台积电为例 , 由于台积电是ASML的大股东之一 , 而且台积电又是ASML最大的客户 , 所以都会将EUV光刻机优先发货给台积电 。

这有助于台积电顺利推进行业领先的工艺技术 , 可以尽早通过最先进的半导体设备去检测 , 生产工艺芯片 。

从7nm开始 , 台积电正式使用EUV光刻机造芯片 , 一直到5nm都是十分顺利的 , 每一个技术节点都在顺利推进 。 甚至到了4nm , 台积电也实现稳定量产 , 良率工艺远远超过了另一个掌握4nm工艺的三星 。

按照台积电的预期 , 会在今年下半年量产3nm , 且台积电过往多次表示3nm会如期进行 。

这给了市场和台积电的客户们很大的期望 , 毕竟台积电一直以来都是稳步前行 , 没有遇上太大的问题 。 但是在2月23日的一则消息中却显示:台积电3nm工艺遭遇良品率难题 。

这则消息报道中提到 , 台积电提升3nm工艺良率仍存在困难 , 正在不断修正 。 如果持续 , 可能会影响客户的生产计划 。

目前这一消息并未得到台积电官方的证实 , 在此之前台积电一直表示3nm工艺会按计划进行 , 公布的工艺路线图中也是指向今年下半年量产 。 那么这则消息和ASML有什么关系呢?如果消息属实 , 那么EUV光刻机的“隐疾”正在凸显 。

众所周知EUV光刻机可以生产7nm , 5nm等高端制程的芯片 , 甚至是量产3nm的关键设备 。 7nm到5nm使用EUV光刻机生产芯片一直没有大问题 , 可到了准备量产3nm的前夕 , 却传来3nm良率遇上难题的消息 。 而这很可能和EUV光刻机的随机效应有关 。

针对EUV光刻机 , 业内一直有一个担忧 , 就是EUV光刻机的随机效应会导致3nm及以下的工艺良率难以提升 。

因为EUV光刻机在光刻芯片的过程中 , 并不是说每次步骤产生的效应都是一样的 。 比如在光子撞击光刻胶时 , 即便操作步骤完全一样 , 可是出现的反应却是随机的 。 制程越先进 , 随机效应越强 。

如果还不明白 , 可以再做一个更直观的假设 。 一颗乒乓球从固定的位置掉落地面 , 同样的空间环境背景下 , 即便落点位置相同 , 可乒乓球却会向不同的地点随机转变 , 这个过程不可预测 。

乒乓球掉落过程就好比随机效应中的某个步骤 , 芯片制造节点越高 , 越要求乒乓球掉落在自己想要的位置 。 可能尝试几十次才能成功一次 , 成功的次数越高 , 则良率越高 。

可是因为随机效应的不可预测 , 让芯片制造商在提升良率时遇上了困难 , 这也就是EUV光刻机的“隐疾” 。 如今这种隐疾和台积电传来3nm工艺良率难提升的消息相呼应 , 恐怕不得不引起重视了 。

ASML , 芯片制造商们该如何应对呢?既然已经找到了隐疾所在 , 那么ASML和芯片制造商们该如何应对呢?难道说一直放任EUV光刻机随机效应的存在 , 而不去解决吗?

作为影响先进芯片制造生产的问题 , ASML和芯片制造商们肯定不会无动于衷 。 虽然随机性不可预测 , 但是却也能找出一些应对之法 。

比如建设模拟运算模型 , 若是能在随机效应体现最明显的步骤环节中建设模拟运算 , 分析出具体的模型走向路线 , 在随机效应发生之前 , 尽量判断出每一种可能出现的随机反应 。 压缩随机反应产生的效果 , 从而供应多种解决方案 。

类似于将乒乓球的掉落位置固定在某个区域内 , 这样在有限的随机反应范围内 , 越能够准确判断出它的落点位置 。

- 院士开讲|这位给战斗机造“心脏”的87岁院士在抖音开讲,硬核知识引700万网友在线学习

- 黑客组织|英伟达“被黑”后续:黑客组织正在出售 GA102/104 LHR 解锁算法

- 笔记本电脑|2022游戏圈“神仙打架”?想要高画质畅玩,还得看RTX30系游戏本

- 红餐网|曾经“高大上”的西餐,正在被年轻人抛弃

- 处理器|华为春季发布会,7款新品,“杀”疯了!

- 陶瓷|高端手机贵在哪里?竟都不是“面儿”上的东西!

- 上市公司|“风投教父”坠落

- 行业|从「狂奔」到「稳步」,看服务机器人“生存指南”

- 除草|小红书“除草”争议背后,斗法、误伤、平衡术

- 品牌|2022年了,玩好私域电商必须掌握的五大商业“须知”