再添最强eASIC!Intel付得起xPU的巨额尾款吗?

一波还未平息 , 一波再起 , 时隔一周 , Intel继续扩张其xPU阵营!

上回 , 笔者说道Intel正在利用xPU+oneAPI的超异构计算的形式延续摩尔定律 。 所谓xPU即为CPU+GPU+FPGA+其他加速器的异构计算 , 体现在数据中心的实际产品便是Xeon可扩展处理器+Xe独立显卡+AGILEX/STRATIX FPGA+SmartNIC加速器+ Movidius VPU 。 针对xPU此前Intel发布了独立服务器GPU和oneAPI Gold 。

实际上 , Intel的FPGA远不是“单枪匹马作战”的单一产品 , Intel在FPGA上其实是依次从FPGA、eASIC过渡到ASIC的全套解决方案 , Intel称这种独特的方案为“定制逻辑连续体” , 仅在FPGA上便是一个“小生态” 。

11月18日 , IFTD2020上 , Intel发布首款用于5G、人工智能、云端与边缘的eASIC N5X(结构化ASIC) , 同时发布了最新的Intel开放式FPGA堆栈(Intel OFS) , 21ic中国电子网采访人员受邀参加此次发布会 。

eASIC究竟是什么FPGA和ASIC一直以来是半导体行业争论不休的话题 , 甚至也频繁出现一者将完全替代另一者的传言 。 事实上 , 两者的存在并不存在任何冲突 。

诚然 , ASIC在计算性能、功耗、可靠性、体积和制造成本上拥有一定优势 。 但从底层来说 , 其内核执行外的任何算法都是冻结的 , 因此这就需要在流片上市之前进行颇为耗时的设计和测试 , 并且一旦流片算法和逻辑电路后都是无法修改的 。 所以ASIC设计通常是定制化 , 目的明确的 。 从侧面来说 , 这就无形增加了前期的投入成本 , 即一次性工程费用(NRE)高 , 并且由于流片后无法修改所以不具备灵活性 。

正因如此种种束缚 , FPGA应运而生 , 可重复编程性加速了产品的上市时间 , 也因其自身的灵活性和适应性拥有了一席之地 。 不过FPGA相对ASIC来说 , 是利用数百万个逻辑单元换取这种便利性的 , 相比来说价格很容易昂贵 。 但并不能因此就绝对说FPGA比ASIC贵 , ASIC的一次性工程费用贵 , 流片量如果太小绝对是成本更高的 。

所以在现阶段 , FPGA和ASIC是“分工明确”的 , 可编程FPGA主要针对实施与加速要求最苛刻的算法阶段 , 直到算法已经非常成熟、并且最终确立下来之后 , ASIC便可大面积实施在硬件之中 。

既然明白FPGA和ASIC的定位 , 那么这个eASIC究竟是什么?eASIC又名为结构化ASIC , 简言之eASIC就是FPGA和ASIC的中间体 , 不过名字既然都只是ASIC加了e , 相比来说还是更靠近ASIC的 。

eASIC与ASIC最大的不同之处就在于在客户购买定制芯片后 , 还能够通过重新编程将芯片不同部分重新连接从而完成新的任务 。 客户可以使用FPGA创建设计将固定布局烘焙到单个设计掩模中 , 最终eASIC也将不再可编程 , 从而获得近似ASIC的功耗性能 。 市场中还存在eFPGA这种产品 , 当然在使用上则会更靠近FPGA , 主要是将ASIC进行片上连接 , 此处不进行详细讲解 。

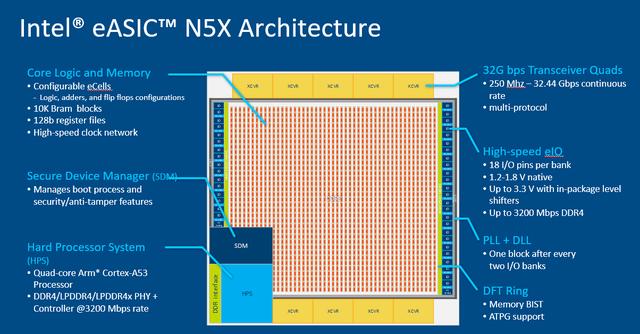

业界最强大的eASIC纵览Intel的eASIC之路 , 此前包括eASIC N2X/N3X/N3XS几种产品 。 而本次发布的eASIC N5X可谓是“天之骄子” , 凝结了多项intel的创新成果 , 不负众望地成为了业界最强大的eASIC 。 这款产品继承了Agilex FPGA的硬核处理器系统、安全特性 , 支持Agilex FPGA用于管理启动、身份验证和防篡改特性的安全设备管理器 , 采用了Diamond Mesa SoC技术 。 文章插图

文章插图

从参数来看 , eASIC N5X使用了16nm制程 , 拥有8千万个ASIC门 , 拥有225Mb双端口存储器 , 32Gbps收发器 , 包含一个四核Arm Cortex-A53硬处理器 。

从性能来看 , eASIC N5X相比AgilexFPGA核心功耗降低了50% , 不仅有效减小了散热 , 还支持客户在同样散热范围内提升性能;相比ASIC , eASIC N5X又拥有更低的总体拥有成本 , 因为这款产品可以加快产品上市速度并显著降低一次性工程费用 。 文章插图

文章插图

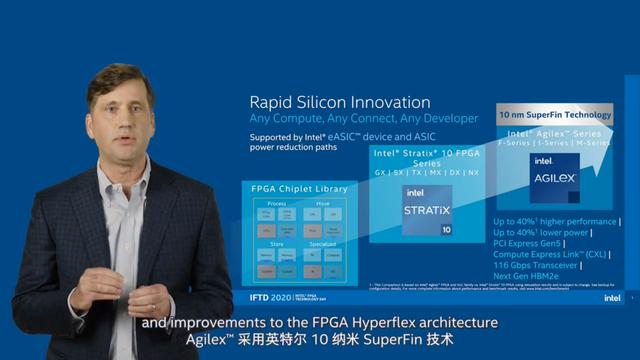

【再添最强eASIC!Intel付得起xPU的巨额尾款吗?】这意味着什么?要知道 , Agilex FPGA系列可是intel的“心头肉” , eASIC N5X的功耗就这么轻松超越了 。 Agilex FPGA是第二代使用异构FPGA chiplet架构的产品 , 这是一种将多种制程技术、功能甚至供应商集成到一种封装的技术 。 Agilex FPGA不仅采用了10nm SuperFin技术和改进的FPGA Hyperflex 架构 , 性能提升了高达 40% , 功耗降低了高达 40% 。 其余的 , 两倍的数据速率 , 支持PCI Express Gen 5和CXL都能说明Intel对这款FPGA的厚望 。 文章插图

文章插图

在设计方面 , 上文也有提及eASIC实际可以直接使用FPGA设计软件进行设计 。 Intel这方面的软件则是Quartus Prime , 这款软件提供了功耗优化工具 , 并通过全面的设计套件帮助轻松提升工作负载性能 。

- 部长|工信部指导,24位院士、9家行业巨头发起,国内最强物联网联盟成立

- 滴滴|“最强之车”已在阵中?聊聊滴滴定制网约车比亚迪D1

- Pro|iQOO 5 Pro 120W超快闪充揭秘:最强快充名不虚传

- Axon|中兴倪飞:Axon 30将搭载业界最强悍且首创影像功能

- 今日|“舜网”学习强国号今日上线 济南报业全媒体矩阵再添新成员

- 一丁|1亿像素手机再添一丁,预定量超10万台,1599元起

- 成员|千元机中的实力派再添新成员,三部千元机,一部更比一部强!

- 中兴倪飞:Axon 30将搭载业界最强悍且首创影像功能

- 打败特斯拉的“最强代步车”诞生?日销超千台,股价飙涨60%

- 宁可花五千多买iPhone12丐中丐,也不买小米最强机?