「计算机组成原理」:现代存储器的结构

按照在计算机中作用的不同 , 存储器分为缓冲存储器、主存、辅助存储器 。 按照存储信息的材料或介质可以分为磁带存储器.磁盘存储器、半导体存储器、光盘存储器 。

理想状态中 , 我们将存储器系统视为一个线性字节数组 , CPU能在常数时间内访问每个存储器位置 。 但实际上存储器系统(Memory System)是一个具有不同容量、成本和访问时间的存储设备的层次结构 , 分别具有以下几部分:

- CPU中的寄存器保存最常使用的数据 , 能在0个时钟周期内访问

- 高速缓存存储器(Cache Memory)是靠近CPU的、较小的快速存储器 , 保存一部分从主存储器(Main Memory)取出的常用指令和数据 , 能在4~75个时钟周期内访问

- 主存缓存存储磁盘上的数据 , 需要上百个时钟周期访问

- 磁盘存储通过网络连接的其他机器的磁盘或磁带上的数据 , 需要几千万个周期进行访问

存储器的层次结构之所以有效 , 是因为程序具有局部性(Locality)的基本属性 , 倾向于不断访问相同的数据项集合 , 或者倾向于访问相邻的数据项集合 。 我们希望程序能具有更好的局部性 , 使得数据项存储在较高层次的存储器中 , 这样程序就会倾向于从存储器结构中较高层次访问数据项 , 运行会更快 。

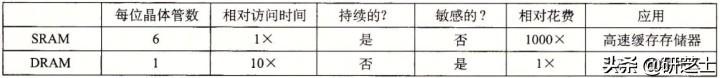

1 存储技术1.1 随机访问存储器随机访问存储器(Random-Access Memory , RAM)根据存储单元实现方式可以分为两类:静态的RAM(SRAM)和动态的RAM(DRAM) 。

文章插图

文章插图1.1.1 SRAM

- 将每个位保存到由6个晶体管电路构成的双稳态的(Bistable)存储器单元 。

- 属性:可以无限期地保持在两个不同的电压配置或状态之一 , 而其他的都是不稳定状态 , 会迅速转移到两个稳定状态之一 。

- 特点:由于具有双稳态 , 所以只要有电 , 就会永远保持它的值 , 即使有干扰 , 当干扰消除时就会恢复到稳态 。

1.1.2 DRAM

- 将每个位保存为 , 对一个由访问晶体管控制的电容的充电 。

- 特点:由于每个存储单元比较小 , DRAM可以制造的十分密集 , 可以作为主存或图形系统的帧缓冲区 。 由于通过电容电压来保存位 , 当电容电压受到扰动时就无法恢复了 。 并且电容存在漏电现象 , 存储单元10~100毫秒会失去电荷 , 使得内存系统必须周期性通过读出重写来刷新内存的每一位 。 暴露在光线中会导致电容电压改变 。

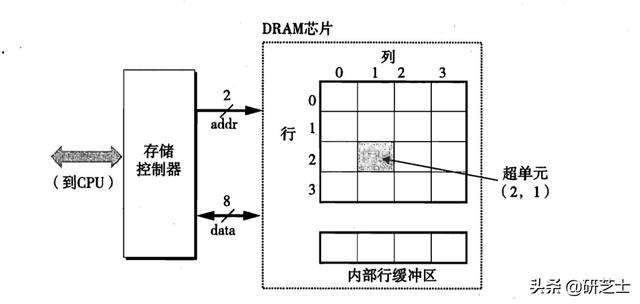

文章插图

文章插图如上图所示 , 我们有一个16 \times 816×8的DRAM芯片 , 其中包含16个超单元 , 每个超单元由8个DRAM单元组成 , 使得每个超单元能存储8位信息 。 并且16个超单元被组成4行4列的阵列形式 。 由一个内存控制器(Memory Controller)通过addr引脚和data引脚将控制DRAM芯片数据的传入和传出 , 比如想要获得(2,1)处超单元的数据

- 内存控制器发送行地址(Row Access Strobe , RAS)2到DRAM芯片 , 则DRAM芯片会将行2中的整行内容复制到内部行缓冲区 。

- 内存控制器发送列地址(Column Access Strobe , CAS)1到DRAM芯片 , 则DRAM芯片会从内部行缓冲区获得1列的数据 , 将其发送到内存控制器 。

- 内存控制器发送RAS和CAS时 , 使用相同的addr引脚 , 使得必须分两步发送地址 , 会增加访问时间 。

- 如果将16个DRAM单元组织成线性形式 , 则需要4位的地址引脚才能索引到每个超单元 , 但是将其组织成4行4列的阵列形式 , 只需要2位的地址引脚 。

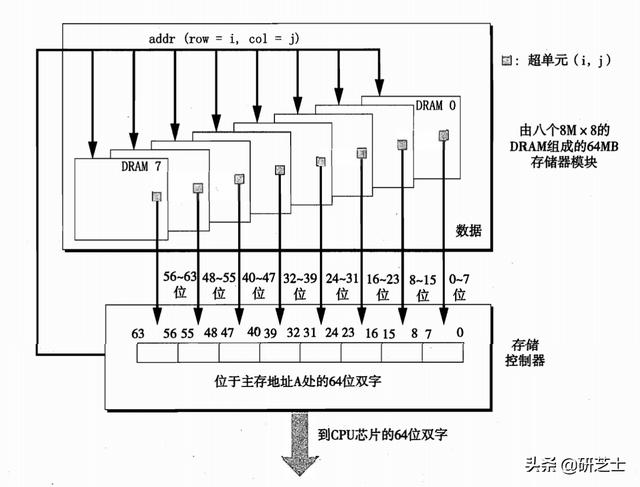

文章插图

文章插图如上图所示是封装了8个 8M \times 88

- 计算机学科|机器视觉系统是什么

- 合并|Andre Cronje主导批量「合并」DeFi项目,是好事情吗?

- mini|电影、mini 与「当日完稿」工作流

- 字化转型|疫情重构经济,传统企业「数字化」的通关密码是什么?

- iPhone12|iPhone12「超大杯」拍照解禁:与Pro拉不开差距

- 供应链|一座快手「重镇」的货端升级

- 项目|DeFi「分叉运动」退潮,我们能从中学到什么?

- 纪念版|「同价选机」K30至尊纪念版 vs Note9 Pro,选谁

- 文案|「热点传递」为什么别人卖点写的“勾人”?

- 系列|OPPO Reno5 真机曝光, 「Reno Glow」晶钻设计再升级