CPU缓存L1/L2/L3工作原理

一、前言

在过去的几年中 , 计算机处理器取得了相当大的进步 , 晶体管的尺寸每年都在变小 , 而且这种进步达到了摩尔定律迅速变得多余的地步 。

当涉及到处理器时 , 不仅晶体管和频率很重要 , 高速缓存也很重要 。

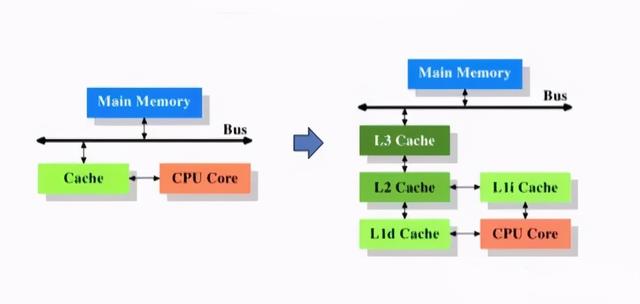

在讨论CPU(Central Processing Units)时 , 您可能听说过高速缓存 。 但是 , 我们并没有过多地关注这些数字 , 它们也不是这些CPU广告的主要亮点 。 文章插图

文章插图

那么 , CPU缓存到底有多重要 , 它又是如何工作的?

二、什么是CPU缓存?

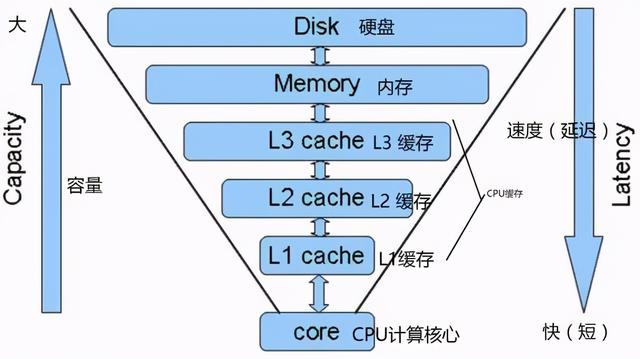

首先 , 缓存只是一种非常快速的内存类型 。 您可能知道 , 计算机内部有多种内存类型 。 有一个主存储(如硬盘或SSD) , 用于存储大量数据(操作系统和所有程序) 。 文章插图

文章插图

接下来 , 我们有随机存取存储器 , 通常称为RAM 。 这比主存储要快得多 。 文章插图

文章插图

最后 , CPU自身具有更快的存储单元 , 我们称之为缓存 。

计算机的内存具有基于速度的层次结构 , 而缓存位于该层次结构的顶部 , 是最快的 。 它也是最靠近中央处理的地方 , 它是CPU本身的一部分 。

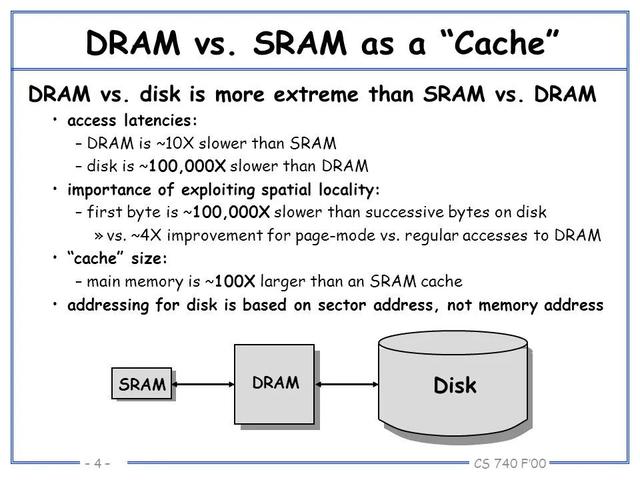

高速缓存是静态RAM(SRAM) , 而系统RAM是动态RAM(DRAM) 。 静态RAM是一种可以保存数据但是不要用一直刷新的存储器 , 与DRAM不同 , SRAM更加适合用于高速缓存 。 文章插图

文章插图

三、CPU缓存如何工作?

我们已经知道 , 程序被设计为一组指令 , 最终由CPU运行 。

当我们运行程序的时候 , 这些指令必须从主存储器取指令到CPU 。 这是内存层次结构起作用的地方 。

数据首先被加载到RAM中 , 然后被发送到CPU 。 因为CPU每秒都能够执行大量指令 。 为了充分利用其功能 , CPU需要访问超高速内存 , 这是缓存的来源 。

内存控制器执行从RAM中获取数据并将其发送到缓存的工作 。 根据系统中使用的CPU , 此控制器可以位于主板的北桥芯片组上 , 也可以位于CPU本身内部 。

然后 , 高速缓存在CPU内执行数据的来回传输 。 内存的层次结构也存在于缓存中 。

四、缓存级别:L1 , L2和L3

CPU缓存分为三个主要的级别 , 即L1 , L2和L3 。 这里的层次结构是根据缓存速度来划分的 。 文章插图

文章插图

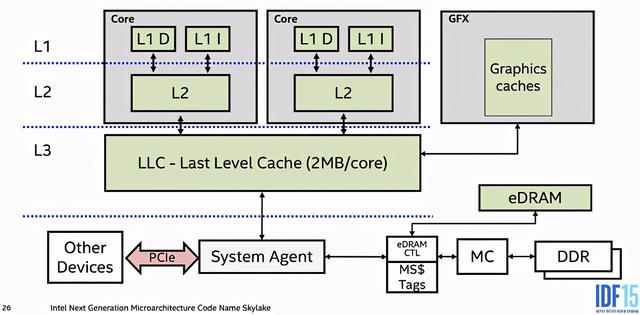

L1(1级)高速缓存是计算机系统中存在的最快的内存 。 就访问优先级而言 , L1缓存具有CPU在完成特定任务时最可能需要的数据 。

就其大小而言 , L1高速缓存通常最多可达256KB 。 但是 , 一些真正功能强大的CPU现在将其占用近1MB 。 现在 , 某些服务器芯片组(如Intel的高端Xeon CPU)具有1-2MB的一级缓存 。

L1缓存通常也分为两种方式 , 分为指令缓存和数据缓存 。 指令高速缓存处理有关CPU必须执行的操作的信息 , 而数据高速缓存则保留要在其上执行操作的数据 。 文章插图

文章插图

L2(2级)缓存比L1缓存慢 , 但大小更大 。 它的大小通常在256KB到8MB之间 , 尽管更新 , 功能强大的CPU往往会超过此大小 。 L2高速缓存保存下一步可能由CPU访问的数据 。 在大多数现代CPU中 , L1和L2高速缓存位于CPU内核本身 , 每个内核都有自己的高速缓存 。

L3(3级)高速缓存是最大的高速缓存存储单元 , 也是最慢的一个 。 它的范围从4MB到50MB以上 。 现代CPU在CPU裸片上具有用于L3高速缓存的专用空间 , 并且占用了很大一部分空间 。

五、缓存命中或未命中以及延迟

数据会从RAM依次流到L3高速缓存 , 然后是L2 , 最后是L1 。

当处理器正在寻找要执行操作的数据时 , 它首先尝试在L1高速缓存中找到它 。 如果CPU能够找到它 , 则该情况称为高速缓存命中 。 然后 , 它继续在L2和L3中找到它 。

如果找不到数据 , 它将尝试从主内存访问数据 。 这称为高速缓存未命中 。

现在 , 众所周知 , 高速缓存旨在加快主内存和CPU之间的数据传输 。

从内存访问数据所需的时间称为延迟 , L1具有最低的延迟 , 是最快的 , 并且最接近核心 , 而L3具有最高的延迟 。 缓存未命中时 , 延迟会增加很多 。 这是因为CPU必须从主存储器中获取数据 。

随着计算机变得越来越快和越来越好 , 我们看到延迟减少了 。 现在 , 我们拥有低延迟的DDR4 RAM , 以及具有低访问时间的超高速SSD作为主要存储 , 这两项都大大降低了整体延迟 。

- 车轮旋转|牵引力控制系统是如何工作的?它有什么作用?

- 副局长|杨林副局长在美团总部调研网络食品安全监管工作

- 临高|元老院快报:《临高启明》重新上架!今后工作如何展开?

- 脸上|那个被1亿锦鲤砸中的“信小呆”:失去工作后,脸上已无纯真笑容

- mini|电影、mini 与「当日完稿」工作流

- 推广|Josh Elman加盟苹果 负责开发者关系与软件推广工作

- 工作|有人说不给差评是善良,有人说给差评是我正常的权利

- 新媒体工作室|勇当政法新媒体高质量发展排头兵,曲阜检察团队风采展

- 一把沙子制作的CPU卖几千块,为什么我们造不出来?

- 执行SEO计划前的准备工作