文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

什么是PPL?PLL是一种反馈控制电路 , 其特点是利用外部输入的参考信号控制环路内部震荡信号的频率和相位 。

Quartus II软件提供了锁相环PLL的IP核 , 对时钟网络进行系统级的时钟管理和偏移控制 , 具有时钟倍频、分频、相位偏移和可编程占空比的功能 。

创建PPL的IP核1、创建新建工程参照新建例程

2、工具栏添加IP核

“菜单栏 - Tools - MegaWizard Plug-In Manage”3、配置IP核运行环境

选择目的 , 由于新创IP核 , 故选择“Create”

选择PLL核

配置PLL核运行环境 , 即可点击“Next”芯片为“Cyclone IV E”系列编程语言为Verilog HDL

- 参数设置

速度等级一般设置为8;

输入时钟频率 , 为50MHz

PLL类型 , 在“Cyclone IV E”系列中只有一个选择

正常模式:

在标准模式下 , PLL对GCLK网络所产生的延迟进行完全补偿 。 正常模式中的内部时钟是与输入时钟管脚相位对齐的 。 在此模式中 , 外部时钟输出管脚会产生相对于时钟输入管脚的相位延迟 。 因此 , 这种模式一般用于产生FPGA内部用时钟 , 不将时钟输出给FPGA外部使用 。

源同步模式:

如果数据和时钟同时到达输入管脚 , 那么在I/O单元输入寄存器的数据与时钟端口 , 数据与时钟之间的相位关系保持不变 。 此模式可用于源同步数据传输 , 只要I/O单元上的数据与时钟都使用同一I/O标准 , 这两个信号就会经历类似的缓冲器延迟 。

零延迟缓冲模式:

在该模式下 , 外部时钟输出管脚与时钟输入管脚是相位对齐的 , 没有延迟 。 当使用该模式时 , 需要在输入时钟与输出时钟上使用同一I/O标准 , 以确保输入与输出管脚上的时钟对齐 。 因此 , 这种模式一般用于FPGA给外部输出时钟信号 。

无补偿模式:在该模式下 , PLL不对任何时钟网络进行补偿 。 这种模式能提供更佳的抖动性能 , 因为反馈到PFD中的时钟不经过某些电路 。 相对PLL输入 , PLL内部以及外部时钟输出均有相位偏移 。 因此 , 一般不选用这种模式 。

输入输出信号配置输入信号:默认给锁相环添加异步复位输出信号:默认输出添加锁信号“lock”

频谱与带宽配置默认即可

时钟转换配置一般只有一个外部晶振 , 默认即可

动态配置PLL一般PLL配置后不会修改 , 暂时默认 。

输出时钟配置启用时钟 , 勾选“Use this clock” , 否则不勾选 。 设置C0为100MHz设置C1为10MHz

添加仿真库

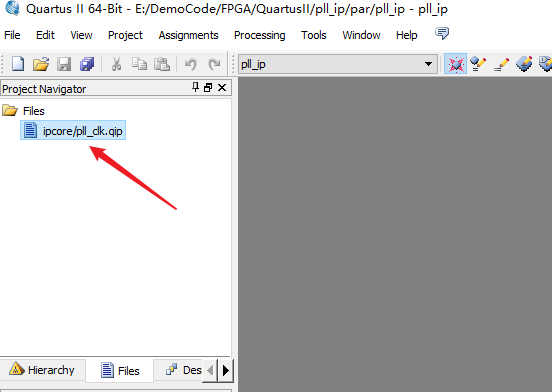

IP核总结页面9.将配置的IP核添加到工程中 , 选择“YES” 。 添加到工程 。

2、添加编写顶层文件 , 然后分析综合

3、分配引脚