SPI协议详解( 二 )

通常情况下, 我们只需要对上图所描述的四个管脚(pin) 进行编程即可控制整个 SPI 设备之间的数据通信:

SCK, Serial Clock, 主要的作用是 Master 设备往 Slave 设备传输时钟信号, 控制数据交换的时机以及速率;

SS/CS, Slave Select/Chip Select, 用于 Master 设备片选 Slave 设备, 使被选中的 Slave 设备能够被 Master 设备所访问;

SDO/MOSI, Serial Data Output/Master Out Slave In, 在 Master 上面也被称为 Tx-Channel, 作为数据的出口, 主要用于 SPI 设备发送数据;

SDI/MISO, Serial Data Input/Master In Slave Out, 在 Master 上面也被称为 Rx-Channel, 作为数据的入口, 主要用于SPI 设备接收数据;

SPI 设备在进行通信的过程中, Master 设备和 Slave 设备之间会产生一个数据链路回环(Data Loop), 就像上图所画的那样, 通过 SDO 和 SDI 管脚, SSPSR 控制数据移入移出 SSPBUF, Controller 确定 SPI 总线的通信模式, SCK 传输时钟信号 。

3.2 Timing

文章插图

文章插图

上图通过 Master 设备与 Slave 设备之间交换1 Byte 数据来说明 SPI 协议的工作机制.

首先, 在这里解释一下相位和极性的概念

3.2.1 SPI相关的缩写或说法

SPI的极性Polarity和相位Phase , 最常见的写法是CPOL和CPHA , 不过也有一些其他写法 , 简单总结如下:

CKPOL (Clock Polarity) = CPOL = POL = Polarity = (时钟)极性

CKPHA (Clock Phase) = CPHA = PHA = Phase = (时钟)相位

SCK=SCLK=SPI的时钟

Edge=边沿 , 即时钟电平变化的时刻 , 即上升沿(rising edge)或者下降沿(falling edge)

对于一个时钟周期内 , 有两个edge , 分别称为:

Leading edge=前一个边沿=第一个边沿 , 对于开始电压是1 , 那么就是1变成0的时候 , 对于开始电压是0 , 那么就是0变成1的时候;

Trailing edge=后一个边沿=第二个边沿 , 对于开始电压是1 , 那么就是0变成1的时候(即在第一次1变成0之后 , 才可能有后面的0变成1) , 对于开始电压是0 , 那么就是1变成0的时候;

3.2.2 SPI的相位和极性

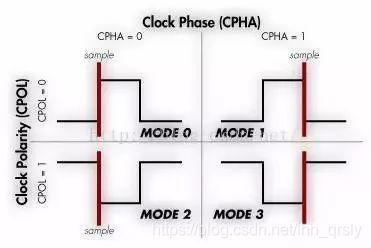

CPOL和CPHA , 分别都可以是0或时1 , 对应的四种组合就是:

Mode 0 CPOL=0, CPHA=0

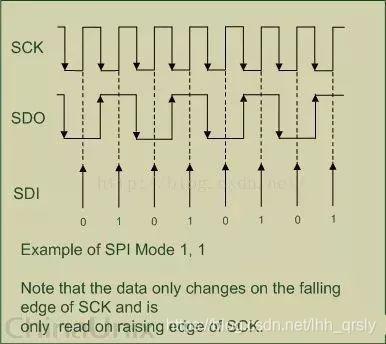

Mode 1 CPOL=0, CPHA=1

Mode 2 CPOL=1, CPHA=0

Mode 3 CPOL=1, CPHA=1

文章插图

文章插图

3.2.3 CPOL极性

先说什么是SCLK时钟的空闲时刻 , 其就是当SCLK在数发送8个bit比特数据之前和之后的状态 , 于此对应的 , SCLK在发送数据的时候 , 就是正常的工作的时候 , 有效active的时刻了 。

先说英文 , 其精简解释为:Clock Polarity = IDLE state of SCK 。

再用中文详解:

SPI的CPOL , 表示当SCLK空闲idle的时候 , 其电平的值是低电平0还是高电平1:

CPOL=0 , 时钟空闲idle时候的电平是低电平 , 所以当SCLK有效的时候 , 就是高电平 , 就是所谓的active-high;

CPOL=1 , 时钟空闲idle时候的电平是高电平 , 所以当SCLK有效的时候 , 就是低电平 , 就是所谓的active-low;

3.2.4 CPHA相位

首先说明一点 , capture strobe = latch = read = sample , 都是表示数据采样 , 数据有效的时刻 。 相位 , 对应着数据采样是在第几个边沿(edge) , 是第一个边沿还是第二个边沿 , 0对应着第一个边沿 , 1对应着第二个边沿 。

对于:

CPHA=0 , 表示第一个边沿:

对于CPOL=0 , idle时候的是低电平 , 第一个边沿就是从低变到高 , 所以是上升沿;

对于CPOL=1 , idle时候的是高电平 , 第一个边沿就是从高变到低 , 所以是下降沿;

- 苏州|阿里巴巴“一基地四中心”落地苏州 双方签署全面合作协议

- 免打扰模式详解

- Dubbo—SPI及自适应扩展原理

- 详解深度学习感知机原理

- Linux基础入门vim常用命令详解

- 德州点创教育:经典FOR循环打印星号三角形算法详解

- 程序员必备的基本算法:递归详解

- 理解 Linux网络栈(1):Linux 网络协议栈简单总结

- 光线|第二代光追究竟有哪些提升?来看详解

- 详解m3u8协议