苹果A14处理器裸片(Die)显微分析:未达到台积电宣称的晶体管密度

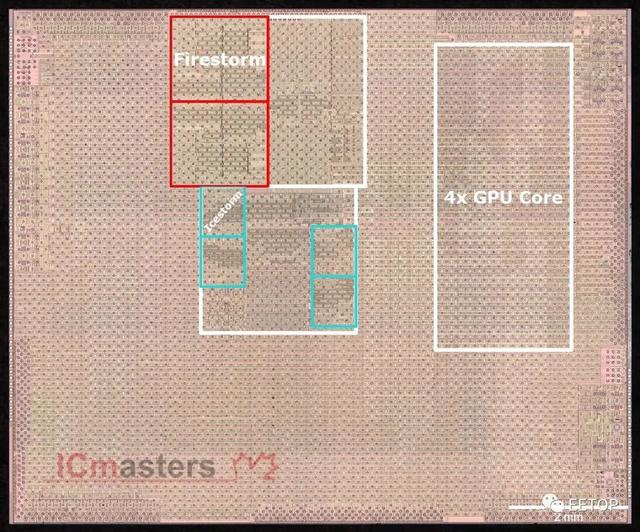

最近国外半导体逆向工程和IP服务公司ICmasters使用透射电子显微镜(TEM)对Apple的A14仿生芯片系统(SoC)进行了初步分析 。 揭开了A14裸片(Die)的神秘面纱 。 文章插图

文章插图

裸片尺寸为88mm2 , 尽管封装了118亿个晶体管 , 但由于采用了台积电的5nm工艺节点 , 芯片尺寸小得令人难以置信 。 而A13仿生处理器的芯片尺寸为98.48mm2 。 虽然图像的质量不是很高 , 但通过粗略的napkin计算 , 我们可以得出 , 具有较大L2缓存的双核FireStorm复合体约为9.1mm2 , 而具有较小L2缓存的四核IceStorm复合体约为6.44mm2, GPU约为11.65mm2 。 我们知道苹果近年来使用了统一的系统缓存 , 但是在图像上很难找到它 。 文章插图

文章插图

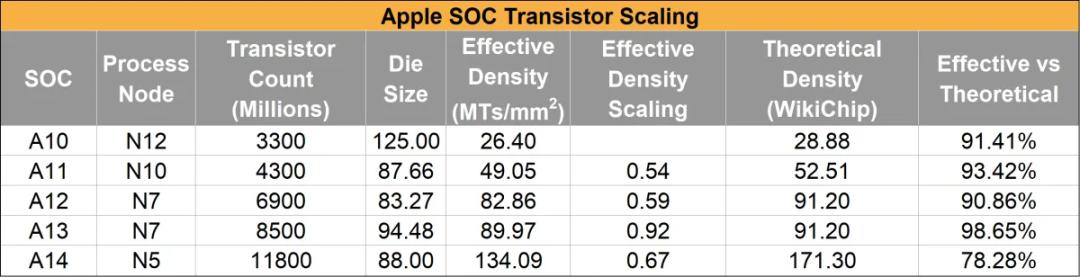

A14 Bionic芯片的平均晶体管密度为1.3409亿个/mm2 , 高于A13 Bionic的0.8997亿个/mm2 。 考虑到半导体厂商在测量晶体管密度时往往使用不同的方法 , 我们无法真正将台积电的N5与英特尔10纳米的约1亿个晶体管/平方毫米进行比较 ,。 同时 , 苹果A14 Bionic的晶体管密度似乎比台积电承诺的基于N5的SoC的理论峰值平均晶体管密度低一些 。 苹果的芯片历史上已经达到了其处理器中进程节点理论密度的90%以上 。 而这一代与理论密度相比 , A14的有效晶体管密度仅为78% 。 尽管台积电声称N5的尺寸缩小了1.8倍 , 但苹果A17仅缩小了1.49倍 。 文章插图

文章插图

之所以没有达到理论缩小倍数 , 主要有以下几种原因:

【苹果A14处理器裸片(Die)显微分析:未达到台积电宣称的晶体管密度】晶体管密度因不同的芯片结构而异 。 逻辑结构可以在每个新节点上很好地扩展 , 但是如今SRAM , I / O和模拟部件很难扩展 , 因此代工厂发布的峰值是高度理论性的 , 而实际数字是取决于设计 。

由于SRAM用于寄存器和缓存 , 因此现代处理器的设计需要占用大量SRAM 。 SRAM需要互连和电路来访问它 , 而此类互连并不总是能够很好地扩展 。 鉴于所有现代SoC都包含不同类型的处理器内核 , 它们也使用高速缓存负载 。

同样 , 芯片的某些部分必须以更高的时钟频率运行(例如 , 通用内核) 。 通过使用通常更大的高性能电池 , 这些零件可能会牺牲性能密度 。 实际上 , 考虑到苹果公司对最终性能的关注 , 其SoC通常具有大容量缓存以及可能进行其他性能优化 。 文章插图

文章插图

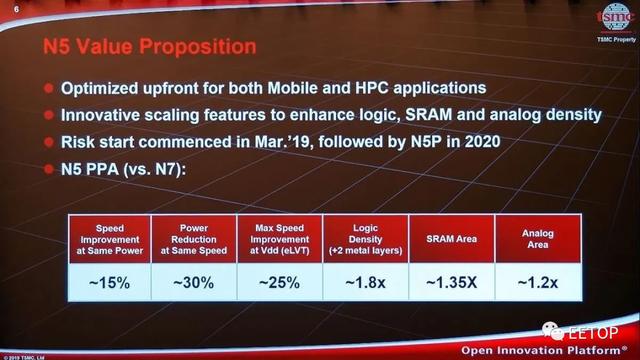

台积电的N5节点与之前的微缩有所不同 , 显示出SRAM扩张放缓的迹象 。 尽管是一个完整的缩小与逻辑 , SRAM是一个1.35倍缩小 , 这个数字被夸大了 。 因此台积电的指引是N5可使晶片面积减少35%-40% 。 半分析预计 , 这将是一个趋势 , 并将持续与新的节点 。 台积电和三星已经在展示3D堆叠SRAM , 这将有助于缓解密度问题 。 文章插图

文章插图

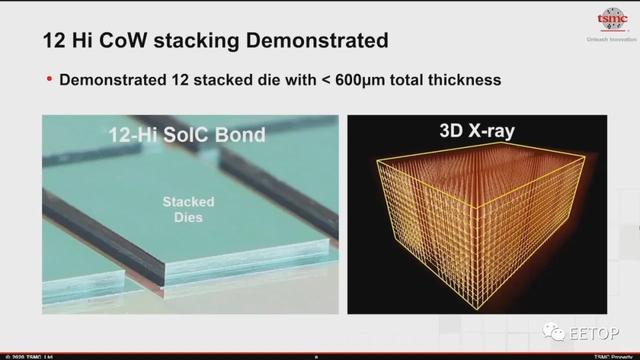

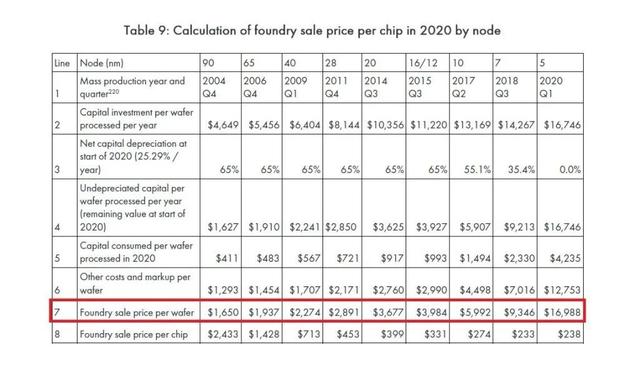

3D堆积并非万能的 , 成本缩减已经开始大幅放缓 。 台积电N5晶圆定价在1.7万美元左右 , 显然每个晶体管的成本并没有下降 。 即使SRAM的缩放速度跟上 , 每晶体管的成本从N7到N5也将保持不变 。 文章插图

文章插图

- 智能手机市场|华为再拿第一!27%的份额领跑全行业,苹果8%排在第四名!

- 无国界|嘴上说着支持华为,却为苹果贡献了2000亿!还真是科技无国界啊?

- iPhone|折叠屏iPhone要来?曝苹果开始测试|OPPO Reno5真机曝光

- iPhone12|“果粉”心灰意冷,苹果iPhone12问题频出,老毛病又犯了

- iPhone|接近8千万!苹果被罚款了!中国iPhone用户这次真的该生气了!

- 误导|苹果又吃巨额罚单,因iPhone防水宣传有误导被重罚9400万

- 打响|拼多多打响双12首枪,iPhone12降到“mini价”,苹果11再见

- 苹果|iPhone13迎来变化!或回归指纹解锁,这几点备受用户喜爱

- 不到|苹果赚了多少?iPhone12成本不到2500元,华为和小米的利润呢?

- 屏幕|苹果iPhone12屏幕不仅发白,还绿的你发慌,用户:环保绿