收购eASIC两年之后,Intel发布首款结构化ASIC产品

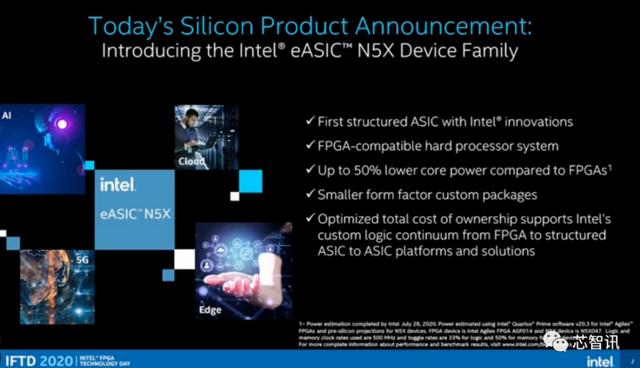

11月18日 , 英特尔在线上举办了“2020英特尔FPGA技术大会” , 正式发布了全新可定制解决方案英特尔eASIC N5X , 将帮助加速5G、人工智能、云端与边缘工作负载的应用性能 。

作为英特尔于2018年收购eASIC之后推出的首款结构化eASIC产品系列 , eASIC N5X搭载了英特尔? FPGA兼容的硬件处理器系统 , 通过FPGA中的嵌入式硬件处理器帮助客户将定制逻辑与设计迁移到结构化ASIC中 , 带来了更低的单位成本 , 更快的性能和更低的功耗等好处 。 文章插图

文章插图

△英特尔首款用于5G、人工智能、云端与边缘的结构化ASIC

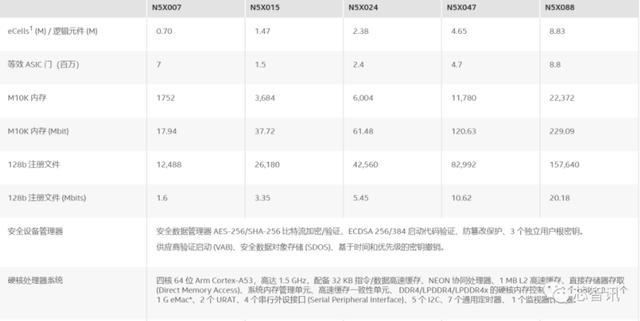

此次英特尔推出的eASIC N5X系列结构化ASIC共有5款产品 , 配备了0.7-8.83百个结构化逻辑元件 , 等效7-8.8百万门ASIC , 同时还集成了四个主频1.5Ghz的64位 Arm Cortex-A53内核 , 以及源自英特尔Agilex FPGA产品系列的具备身份验证和防篡改特性的安全数据管理器 。 文章插图

文章插图

英特尔表示 , 与自己的Agilex FPGA AGF014相比 , eASIC N5X (N5X047)在同样的逻辑时钟频率和内存时钟频率下 , 核心功耗降低了50% , 并且单位成本也降低了50% 。

此外 , 由于在结构化 ASIC中使用预定义基础阵列需要的掩码层自定义和设计步骤更少 , 因此与标准单元ASIC 相比 , NRE(一次性工程费用)更低 , 工程量更少 。 因此 , 相比标准单元ASIC , eASIC N5X可缩短上市时间 , 并降低非经常性工程成本 。

因此 , 用户可以凭借N5X器件快速创建功耗优化、高性能、高度差异化、低成本的解决方案 , 并且可以满足许多应用的关键安全性需求 。

英特尔公司副总裁、可编程解决方案事业部总经理Dave Moore表示: “数据改变行业和商业的潜力从未如此之大 。 英特尔? eASIC N5X给我们的客户带来了独特优势 , 让他们得以同时充分享受英特尔FPGA带来的灵活性和面市速度的优势 , 以及结构化ASIC带来的更低运行能耗的性能效益 。 通过我们称之为‘定制逻辑连续体’的英特尔FPGA、eASIC和ASIC产品组合让客户得以利用数据的潜力 , 这是市场上其它厂商无法做到的 。 ” 文章插图

文章插图

△英特尔公司副总裁、可编程解决方案事业部总经理Dave Moore

夹缝中求生的eASIC迎来新篇章?

众所周知 , FPGA是一种可编程的半定制芯片 , 其与GPU一样具有并行处理优势 , 并且也可以设计成具有多内核的形态 , 当然其最大的优势还是在于其可编程的特性 。 这也意味着用户可以根据需要的逻辑功能对电路进行快速烧录 。 即使是出厂后的成品FPGA的逻辑块和连接 , 用户无需改变硬件 , 就可通过升级软件来配置这些芯片来实现自定义硬件功能 。

但是 , FPGA是用硅片面积来换取灵活性的 , 天生不足表现为资源利用率低、价格昂贵 。 FPGA中的互联使用的是专用可编程连线模块 , 80%的硅片面积被用作布线路由 , 要多绕许多路径 , 要过许多用晶体管搭建的开关 。 将基于SRAM的查找表LUT逻辑单元组成逻辑电路所需要的逻辑层数比直接使用片上金属线做互联的定制化ASIC多 。 因此 , 在速度和功耗上都要比ASIC差很多 。 数据显示 , 同样硅片面积小 , 65nm工艺的FPGA在性能上也只能相当于180nm的ASIC , 而成本上与180nm的ASIC芯片并没有优势 。

相较于及半定制的FPGA来说 , ASIC芯片的计算能力和计算效率都直接根据特定的算法的需要进行定制的 , 所以其可以实现体积小、功耗低、高可靠性、保密性强、计算性能高、计算效率高、成本低等优势 。 当然 , ASIC芯片的缺点也很明显:前期投入费用高昂 , 设计流程复杂 , 风险较高;一旦设计完成 , 流片后就无法再修改逻辑电路 , 缺乏FPGA那样的灵活性;如果无法大量应用的话 , 其整体成本可能比部署FPGA更高 。

为此eASIC公司则试图在标准单元ASIC和FPGA之外中找到另外一条定做芯片的途径 。 所以eASIC推出了半成品的结构化ASIC , 当然要做成客户定制的芯片仍然需要掩模 , 只不过掩模层数少一些 。

总的来说 , 结构化ASIC能够节省一半的NRE费用和设计时间 , 芯片的性能和功耗接近标准单元ASIC 。 但芯片的成本约是标准单元的1.5 ~2倍 , 因为其密度大约只有标准单元ASIC的50%~75%左右 。 结构化ASIC的市场定位决定了其在ASIC与FPGA的夹缝中求生 。

或许是因为半导体工艺升级换代太快了的缘故 , 大多数结构化ASIC的优势还没有来得及完全发挥出来 , 就被新工艺淘汰出局 。 直到在90nm之前 , 大多数结构化ASIC在商业运作上都没有FPGA成功 。 客户要么更喜欢便宜的标准单元ASIC , 要么更喜欢没有风险的随时都可重新编程的器件FPGA 。 除非把做ASIC的NRE降到微不足道 , 还要让设计工程师避开复杂的后端设计的困扰 , 否则难以扭转结构化ASIC尴尬的局面 。

- 王储|壹周游闻第20期:直播打赏实行实名制;沙特王储收购SNK

- 入手|入手不亏的三款5G千元机,款款高性价比,用两年无压力!

- 审查|Facebook超10亿美元收购Kustomer 该交易仍面临审查

- YY|百度收购YY!此前几天,一个山寨横行的时尚品牌logo,卖了137亿

- 跳动|收购支付牌照,字节跳动储备新域名,官方称为防恶意侵权

- 美通社|科睿唯安收购韩国Hanlim IPS | Hanlim

- 华为mate20|899元捡漏华为Mate20,麒麟980+徕卡三摄能再战两年吗?

- 买下|罕见收购!Facebook花10亿多美金买下了一家ToB公司

- 折叠屏|iPhone 外观迎重大更新,还得等两年

- 华为荣耀|被拘两年!孟晚舟引渡聆讯程序何时休?