「正点原子FPGA连载」第三章AXI GPIO控制LED实验

1)实验平台:正点原子达芬奇FPGA开发板

2) 摘自【正点原子】达芬奇之Microblaze 开发指南3)购买链接:4)全套实验源码+手册+视频下载地址:5) 正点原子官方B站:6)对正点原子FPGA感兴趣的同学可以加群讨论:876744900

第三章AXI GPIO控制LED实验

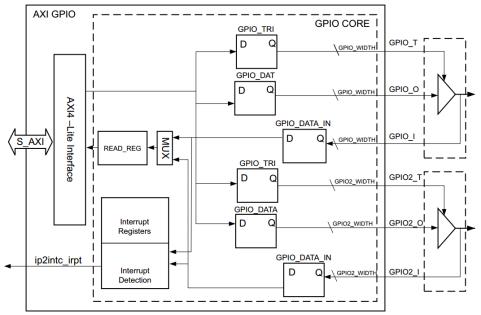

在嵌入式系统中 , 经常需要控制许多结构简单的外部设备或者电路 , 这些设备有的需要通过CPU控制 , 有的需要CPU提供输入信号 。 嵌入式微处理器通常用GPIO控制这些设备 , 本次实验我们将通过AXI GPIO进行LED流水灯实验 。 33.1 简介3.2实验任务3.3硬件设计3.4程序设计3.5下载验证3.1简介AXI GPIO IP核为AXI接口提供了一个通用的输入/输出接口 。 AXI GPIO是一个软核(Soft IP) , 是由用户通过配置芯片的逻辑资源来实现的一个功能模块 。 AXI GPIO可以配置成单通道或者双通道 , 每个通道的位宽可以单独设置 。 另外通过打开或者关闭三态缓冲器 , AXI GPIO的端口还可以被动态地配置成输入或者输出接口 。 其顶层模块的框图如下所示:

文章插图

文章插图

图 3.1.1 AXI GPIO框图

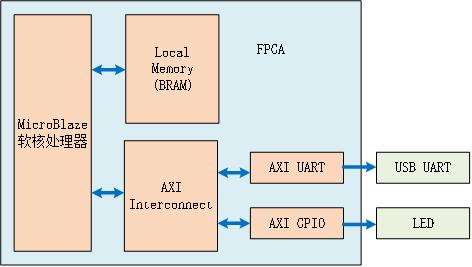

从图 3.1.1可以看到 , 模块的左侧实现了一个32位的AXI4-Lite从接口 , 用于主机访问AXI GPIO内部各通道的寄存器 。 当右侧接口输入的信号发生变化时 , 模块还能向主机产生中断信号 。 不过只有在配置IP核时选择“使能中断” , 才会启用模块的中断控制功能 。 3.2实验任务本章的实验任务是通过调用AXI GPIO IP核 , 实现LED流水灯功能 , 并进行程序固化 , 实现程序上电自启动 。 3.3硬件设计根据实验任务我们可以画出实验系统框图:

文章插图

文章插图

图 3.3.1 系统框图

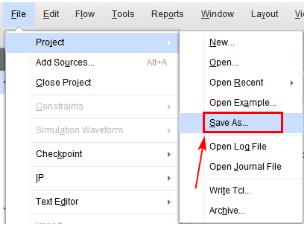

由系统框图可以看出 , AXI GPIO和AXI UART都通过AXI Interconnect模块与MicroBlaze互联 , Microblaze处理器输出LED灯的控制信号 , 通过AXI Interconnect互联模块传输到AXI GPIO模块 , AXI GPIO模块根据AXI4-Lite协议将LED灯控制信号解析出来 , 输出到FPGA的LED引脚 , 从而控制LED灯 。step1:创建Vivado工程本次实验硬件设计可以在《Hello World》实验的基础上进行 , 这里我们就没有必要重新创建工程了 , 此处顺便可以介绍下如何在先前工程的基础上继续实验而不破坏先前的工程 。 我们先打开《Hello World》实验的Vivado工程 , 打开后依次点击菜单栏的“File->Project->Save As...” , 如图 3.3.2所示:

文章插图

文章插图

图 3.3.2 选择另存为

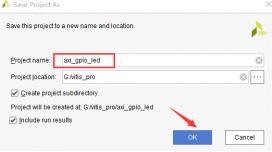

在弹出的另存为界面中可以输入新的工程名或更改保存位置 , 此处我们输入新的工程名“axi_gpio_led” , 工程位置可以选择 , 保持默认即可 , 然后点击“OK”按钮 。 如图 3.3.3所示:

文章插图

文章插图

图 3.3.3 另存为工程为axi_gpio_led

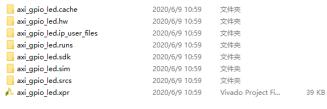

之后 , 如果我们打开工程所在目录G:/vitis_pro/axi_gpio_led , 就会看到如下的目录结构:

文章插图

文章插图

图 3.3.4 axi_gpio_led工程目录

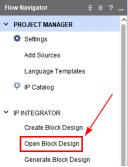

至此 , 在原工程的基础上成功创建了一个新的工程而没有破坏原来的工程 , 也避免了重新创建工程或复制工程后修改的麻烦 。 step2:使用IP Integrator创建Processing System在Flow Navigator中 , 点击IP INTEGRATOR下的“Open Block Design” , 如图 3.3.5所示:

文章插图

文章插图

- 比原子弹还稀有,全球就两国掌握,光刻机为什么如此难造?

- 除了华容网格、原子组件 OriginOS还有什么?

- 星光 | 东大电子科学与工程学院、微电子学院院长孙立涛:借“原子制造”,筑未来电子

- 力鼎华为,以“造原子弹”的体制优势,造“高端光端机”的艰难