STM32CubeMX + HAL库学习「附工程源码」( 三 )

SDRAM

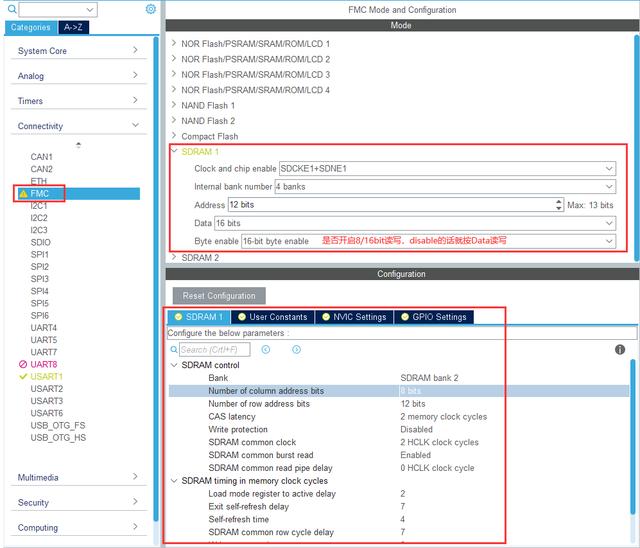

- 开启FMC功能 , Pinout --tt-darkmode-color: #809CB9;">, Connectivity -> FMC -> SDRAM2SDRAM1的起始地址为0XC0000000 , SDRAM2的起始地址为0XD0000000 。 一般SDRAM都含有4个bank 。 Configuration中的参数可从SDRAM的数据手册上找到 。

文章插图

文章插图各个选项的配置(只做解释 , 不对应上图):

- Clock and chip enable:FMC_SDCKE0 和FMC_SDCLK0对应的存储区域1 的地址范围是0xC000 0000-0xCFFF FFFF;而FMC_SDCKE1 和FMC_SDCLK1 对应的存储区域2 的地址范围是0xD000 0000- 0xDFFF FFFF

- Bank由硬件连接决定需要选择SDRAM bank 2

- Column bit number表示列数 , 8位

- Row bit number表示行数 , 12位

- CAS latency表示CAS潜伏期 , 即上面说的CL , 该配置需要与之后的SDRAM模式寄存器的配置相同 , 这里先配置为2 memory clock cycles(对于SDRAM时钟超过133MHz的 , 则需要配置为3 memory clock cycles)

- Write protection 表示写保护 , 一般配置为Disabled

- SDRAM common clock为SDRAM 时钟配置 , 可选HCLK的2分频\3分频\不使能SDCLK时钟 。 前面主频配置为216MHz , SDRAM common clock设置为2分频 , 那SDCLK时钟为108MHz , 每个时钟周期为9.25ns

- SDRAM common burst read 表示突发读 , 这里选择使能

- SDRAM common read pipe delay 表示CAS潜伏期后延迟多少个时钟在进行读数据 , 这里选择0 HCLK clock cycle

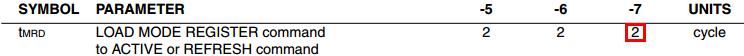

- Load mode register to active delay 加载模式寄存器命令和激活或刷新命令之间的延迟 , 按存储器时钟周期计

文章插图

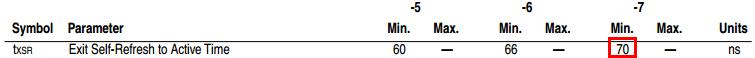

文章插图- Exit self-refresh delay从发出自刷新命令到发出激活命令之间的延迟 , 按存储器时钟周期数计查数据手册知道其最小值为70ns , 由于我们每个时钟周期为9.25ns , 所以设为8 (70÷9.25 , 向上取整)

文章插图

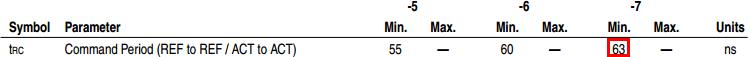

文章插图- SDRAM common row cycle delay刷新命令和激活命令之间的延迟 , 以及两个相邻刷新命令之间的延迟 ,以存储器时钟周期数表示查数据手册知道其最小值为63ns , 由于我们每个时钟周期为9.25ns , 所以设为7 (63÷9.25 , 向上取整)

文章插图

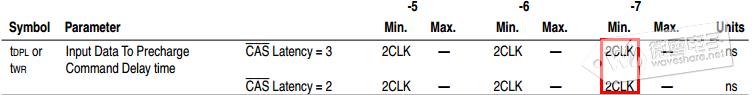

文章插图- Write recovery time写命令和预充电命令之间的延迟 , 按存储器时钟周期数计

文章插图

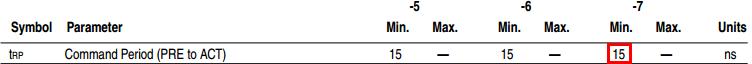

文章插图- SDRAM common row precharge delay预充电命令与其它命令之间的延迟 , 按存储器时钟周期数计查数据手册知道其最小值为15ns , 由于我们每个时钟周期为9.25ns , 所以设为2 (15÷9.25 , 向上取整)

文章插图

文章插图- Row to column delay激活命令与读/写命令之间的延迟 , 按存储器时钟周期数计查数据手册知道其最小值为15ns , 由于我们每个时钟周期为9.25ns , 所以这里本应该设为2 (15÷9.25 , 向上取整)但要注意 , 时序必须满足以下式子:TWR ≥ TRAS - TRCDTWR ≥ TRC - TRCD - TRP其中:TWR = Write recovery time = 2TRAS = Self refresh time = 5TRC = SDRAM common row cycle delay = 7TRP = SDRAM common row precharge delay = 2TRCD = Row to column delay所以这里Row to column delay应该取3

- 假期弯道超车 国美学习“神器”助孩子变身“学霸”

- 想自学Python来开发爬虫,需要按照哪几个阶段制定学习计划

- 未来想进入AI领域,该学习Python还是Java大数据开发

- Google AI建立了一个能够分析烘焙食谱的机器学习模型

- 学习大数据是否需要学习JavaEE

- 学习“时代楷模”精神 信息科技创新助跑5G智慧港口

- 非计算机专业的本科生,想利用寒假学习Python,该怎么入手

- ?优学天下带着学习机冲刺上市,智能教育硬件有多烧钱?

- 数据分析与机器学习:侦测应用内机器人作弊关键

- 打破开发壁垒,2020深度学习开发者峰会百度飞桨认证PPDE分享开源收获