晶体管|超能课堂(242):CPU的功耗是怎么产生的?它的功耗大小与哪些因素有关?

【 晶体管|超能课堂(242):CPU的功耗是怎么产生的?它的功耗大小与哪些因素有关?】作为现今PC平台上的两个能耗大户之一,CPU的功耗问题可谓是牵扯了非常之多的关系户,比如说主板的供电系统要根据CPU的功耗来设计,比如说为CPU散热的散热器要根据CPU的功耗去设计,还有电源要为CPU准备好足够的供电……但你知道CPU的功耗是怎么产生的吗?为什么这么一块小小的芯片要用掉这么多的电能?本文就对CPU功耗产生的原理进行简单的阐述,简单讲述一下CPU的功耗具体都跟哪些因素有关系。首先我们要从构成CPU的基础单元——晶体管开始说起。

文章图片

晶体管的工作方式与功耗是怎么产生的?

大家都知道各种数字电路芯片的基础成员是一个个非常非常小的晶体管,在目前的处理器上面常见的是场效应管(FET),在CPU上比较常见的MOSFET大概长成下面那张图片的样子:

文章图片

当我们在这个晶体管的栅极与源极之间施加电压的时候,能够改变源极与漏极之间的阻抗,从而控制源极到漏极之间的电流大小。利用这种特性,我们可以把多个晶体管组成一个组合,它可以让表示两种信号的电平在通过组合后产生高电平或低电平的信号,高低两种电平可以对应到逻辑上的“真”与“假”,亦可对应二进制中的“1”和“0”。这种晶体管的组合被称为逻辑门,将多个逻辑门组合到一起可以实现更为复杂的逻辑运算。CPU就是由非常多的逻辑门组成的。

那么在CPU工作的时候,组成它的逻辑门状态实际是一直在发生着改变的,此时可以将逻辑门内部的晶体管视为小电容,电容的充放电就引起电能流动,此时就产生了CPU的动态功耗。

为什么说这功耗是动态的呢?因为这部分功耗的大小与CPU的运行状态有关。我们知道,主频是CPU最主要的规格之一,它指的是晶体管在一秒内的开关次数,晶体管开关次数越高,频率也就会更高,但总的充放电次数也同时增加了,于是晶体管的耗电量也就随之增加。

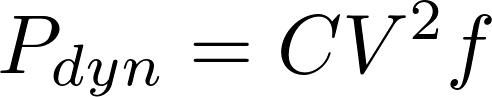

通过实际测算,人们发现CPU的动态功耗与频率成正比,与电压的平方大致成正比,也就可以导出如下的公式:

文章图片

也就是说,CPU的电压越高,频率越高,其动态功耗就会越大。有动态功耗,相对的自然就有静态功耗的概念,这部分主要来自于晶体管的漏电。

让我们回到本节开头的MOSFET结构示意图上,在栅级的下方有一层很薄的氧化层,它起到绝缘的作用。在把晶体管做小的过程中(也就是制程进步的过程中),这个绝缘层的厚度越来越薄,由于量子效应,部分电荷载流子将穿过这薄薄的绝缘层,出现漏电现象。这种漏电现象将增加晶体管的耗电量,虽然单个晶体管的漏电量相当微小,但是当晶体管的数量达到上亿甚至是数十亿级别之后,整个的漏电量就不容小觑了。

除了漏电以外,还有一部分静态功耗是晶体管出现导通情况引起的。在逻辑门状态发生改变的时候,组成它的部分晶体管可能会出现同时导通的情况,也就是短路的情况,此时会产生短路功耗,其大小与逻辑门的大小相关。

综上所述,我们可以把CPU的功耗分成两大类,分别是CPU在运算时产生的动态功耗和CPU在加电时产生的静态功耗,静态功耗中的绝大部分是由晶体管漏电所引起的。因此,我们可将CPU的功耗大小与CPU的主频、规模和制程等因素联系在一起。

制程与功耗的复杂关系

这几年Intel的桌面处理器制程止步不前,14nm++++甚至已经成为一个笑柄,而“Intel处理器功耗相对偏高”这个问题也不断被大家所指出,那么制程跟功耗之间到底有什么样的关联关系呢?

更好的制程能够让处理器设计方在同样的面积内塞入更多的晶体管,更多的晶体管在大多数时候都意味着处理器会有更强的性能,但根据上一节所说的,更多的晶体管会产生更大的静态功耗。另外,更先进的制程并不一定会在控制晶体管漏电率方面较老制程有优势,Intel曾经在从65nm到45nm的演进时为了控制漏电率而引入了新的绝缘材料。

上面说的都是制程对静态功耗方面的影响,再来说说它对动态功耗的影响。更新的制程能够让晶体管做的更小,降低了栅级的电容和阻抗,进而带来的是晶体管开关速度的优化,这能够降低逻辑门切换的延迟,允许处理器将主频提升到一个新的水平上去。但不可忽视的一点在于,提升晶体管开关频率的同时会增加动态功耗,如若我们要提升主频,那就要给晶体管加上更高的电压,让逻辑门切换的延迟跟上主频,更高的电压带来的就是更高的功耗。

所以制程和功耗之间存在复杂的制约关系,制程的提升能够减少晶体管的电能开销,但为了更大幅度地提升性能而扩大芯片规模则会在一定程度上抵消掉制程提升带来的节能效果,另外追逐更高的主频也会产生更多的动态功耗。不过呢,设计CPU的团队一般都会考虑到这些复杂关系,尽可能的利用制程进步带来的好处,而规避掉它的弊端。

不过在我们的实际使用过程中,即便是CPU同样跑到了占用率100%,其功耗还是会有很大的不同。这是为什么呢?简单的说,不同软件或者指令会调用CPU不同的区域,调用的晶体管数量是不同的。分页标题

不同软件/指令下对晶体管的调动

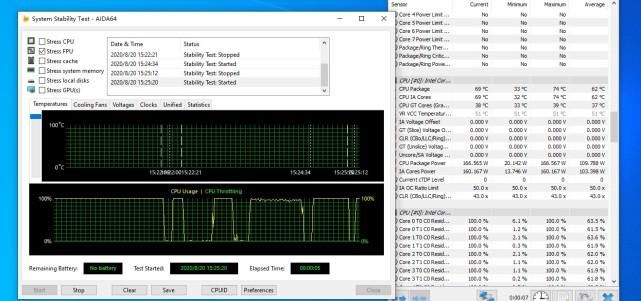

由软件发出的指令经过CPU内核的解码和调度,最终进入到执行单元中被执行。执行单元有不同的种类,部分可能专门负责做加法,一部分可能专门负责做乘法。不同的执行单元在激活时会消耗不同的电能,也就是说,同样一个内核,在调用不同执行单元时其功耗会有很大不同。比如说现在处理器普遍支持AVX指令集,在支持AVX2的处理器上,一条AVX指令最多能够操作的数据宽度是原本SSE指令的两倍(128-bit=>256-bit),那么这就需要更宽的寄存器和执行单元来实现。

文章图片

关闭AVX指令集支持,此时的CPU功耗在133W左右

文章图片

打开AVX指令集支持,此时的CPU功耗在166W左右

文章图片

我们这里用了AIDA64的稳定性测试来简单说明,可以看到在同样使用FPU烤机时,关闭AVX指令的时候CPU功耗比开启时低了约莫有30W。

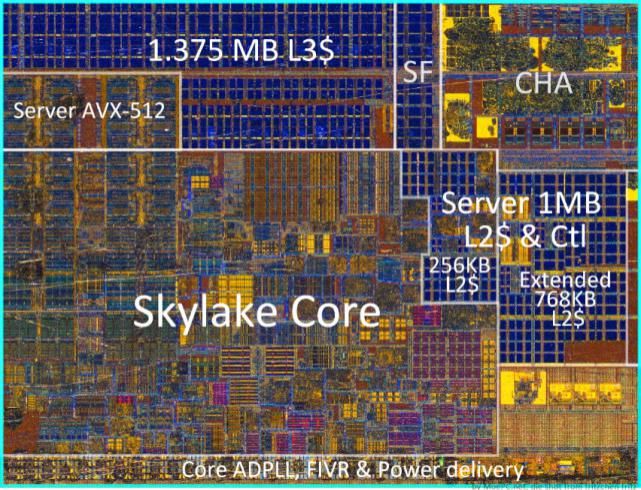

如果要更直观的说明,那不妨来看看服务器版Skylake内核的Die Shot:

文章图片

可以看到服务器版的Skylake内核在左上方有一块Server AVX-512区域,它就是用来支持AVX-512的。结合我们刚才所说的,更多的晶体管会耗更多的电,所以在调用AVX2、AVX-512这些更宽的指令集时,CPU的耗电量也会明显增加。

另外对功耗有影响的是现在x86处理器上面常见的同时超线程技术(SMT),它需要增加一定的晶体管数量,但能够获得比较可观的性能收益,由于超线程技术提升了执行单元的利用率,所以在开启了超线程技术之后,即便处在同样的满载情况下,CPU的功耗也会出现明显的增加。

电源管理策略的影响

处理器的功耗过大时会产生大量的热量,如果散热条件跟不上,那就会因为温度过高而影响晶体管的稳定性。另外在移动平台上,因为受到电池容量的制约,处理器的功耗不宜过大,那处理器该怎么控制自己的功耗呢?

现代处理器上面有各种各样的电源管理技术,比较通行的一种办法是将电源管理交由操作系统来负责。比如处理器厂商会为处理器定义多种电源状态,C-State和P-State就是两种常见的用于描述处理器电源状态的状态值。其中C-State用于节能,P-State用于决定CPU在有负载情况下的电压-频率状态。操作系统来根据当前的负载情况来调整CPU的状态,这样在检测到有高负载任务时,系统会将处理器调整到全速运行状态;在轻负载时,系统会让处理器进入低速状态,甚至将其部分关闭。

另外处理器厂商还加入了很多软硬件结合的节能技术,像是Intel和AMD在很久以前就给CPU引入的SpeedStep/Cool'n'Quiet这些技术都可以让CPU在不损失最大性能的同时,尽可能的节约能耗。现在则是有Speed Shift和Turbo Cove这样的技术接手了。

总结

CPU的功耗主要有动态功耗和静态功耗两大部分组成,前者主要由晶体管不断开关产生的,后者主要由晶体管漏电产生的。CPU那不断扩张的规模会抵消掉制程进步带来的一部分优化。在不同情况下,CPU的功耗表现会有很大不同,这主要是因为不同指令所调用到的晶体管数量是不同的。

为了管好CPU的功耗,CPU厂家也不断为它引入新的电源管理特性。如今的x86 CPU在节能表现上和当初已经不能同日而语了。但由于制程进步越来越困难而我们仍然需要不断扩张的CPU规模来提供更高的性能,所以未来的CPU也不会更为省电,不过它会拥有更好的能效比这一点是肯定的。

- 超能网|NVIDIA RTX 30系列规格曝光,下个月三卡连发

- 社会实践|踏梦用心云支教,川行课堂新创意

- 新冠肺炎_社会|线上线下衔接紧 空中课堂形式新

- 奇趣|综艺 | 龚琳娜《叮咚上线!老师好》展现奇趣音乐课堂

- 明星八卦|王丽坤不忌口一样90斤,生图身材超能打,“水蛇腰”不需要运动

- 聚智|腾讯课堂宣布战略升级并发布“聚智计划”,推动人才高质量就业

- 青少年 社区教育学校 暑期课堂 毕业典礼|龙山街道龙脊新村社区开展青少年“暑期课堂”毕业典礼活动

- 学而思|学而思AI互动课上线智慧屏,华为视频倾力打造家庭智慧课堂

- 课堂|腾讯课堂宣布战略升级:成为综合性终身教育平台

- 聚智|腾讯课堂宣布战略升级并发布“聚智计划” 推动人才高质量就业