技术|IC集成能让相控阵技术发展到什么地步?

半导体技术的进步推动了相控阵天线在整个行业的普及。早在几年前,防务应用中已经开始出现从机械转向天线到有源电子扫描天线 (AESA) 的转变,但直到最近,才在卫星通信和5G通信中取得快速发展。小型AESA具有多项优势,包括能够快速转向、生成多种辐射模式、具备更高的可靠性;但是,在IC技术取得重大进展之前,这些天线都无法广泛使用。平面相控阵需要采用高度集成、低功耗、高效率的设备,以便用户将这些组件安装在天线阵列之后,同时将发热保持在可接受的水平。本文将简要描述相控阵芯片组的发展如何推动平面相控阵天线的实现,并采用示例辅助解释和说明。

在过去几年里,我们在非常重视方向性的场合广泛使用抛物线碟形天线来发射和接收信号。其中许多系统表现出色,在经过多年优化之后保持了相对较低的成本。但这些机械转向碟形天线存在一些缺点。它们体积庞大,操作缓慢,长期可靠性较差,而且只能提供一种所需的辐射模式或数据流。

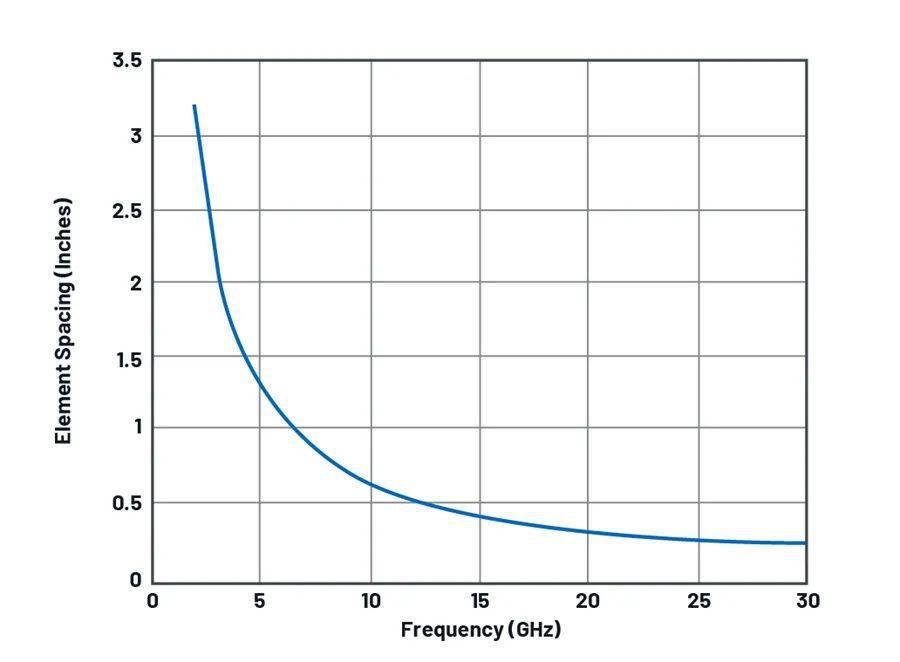

相控阵天线采用电信号转向机制,具有诸多优点,例如高度低,体积小、更好的长期可靠性、快速转向、多波束等。相控阵天线设计的一个关键方面是天线元件的间隔。大部分阵列都需要大约半个波长的元件间隔,因此在更高频率下需要更复杂的设计,由此推动IC在更高频率下,实现更高程度的集成,越加先进的封装解决方案。

人们对将相控阵天线技术应用于各种应用领域产生了浓厚的兴趣。但是,受限于目前可用的IC,工程师无法让相控阵天线成为现实。近期开发的IC芯片组成功解决了这一问题。半导体技术正朝着先进的硅IC方向发展,这让我们可以将数字控制、存储器和RF晶体管组合到同一个IC中。此外,氮化镓 (GaN) 显著提高了功率放大器的功率密度,可以帮助大幅减小占位面积。

相控阵技术

在行业向体积和重量更小的小型阵列转变期间,IC起到了重大的推动作用。传统的电路板结构基本使用小型PCB板,其上的电子元件垂直馈入天线PCB的背面。在过去的20年中,这种方法不断改进,以持续减小电路板的尺寸,从而减小天线的深度。下一代设计从这种板结构转向平板式方法,平板设计大大减小了天线的深度,使它们能更容易地装入便携应用或机载应用当中。要实现更小的尺寸,需要每个IC足够程度的集成,以便将它们装入天线背面。

在平面阵列设计中,天线背面可用于IC的空间受到天线元件间距的限制。举例来说,在高达60°的扫描角度下,要防止出现光栅波瓣,最大天线元件间隔需要达到0.54 λ。图1显示了最大元件间距(英寸)和频率的关系。随着频率提高,元件之间的间隔变得非常小,由此挤占了天线背后组件所需的空间。

文章插图

图1. 阻止在偏离瞄准线60°时产生光栅波瓣的天线元件间隔。

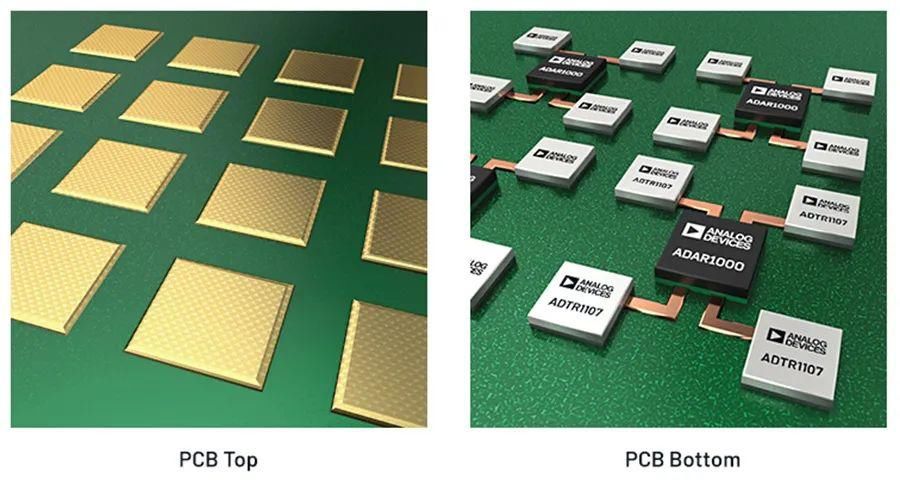

在图2中,左图展示了PCB顶部的金色贴片天线元件,右图显示了PCB底部的天线模拟前端。在这些设计中,在其他层上部署变频级和分配网络也是非常典型的。很明显可以看出,采用更多集成IC可以大幅降低在所需空间内部署天线设计的难度。在我们将更多电子元件封装到更小尺寸内,使得天线尺寸减小之后,我们需要采用新的半导体和封装技术,让解决方案变得可行。

文章插图

图2. 平面阵列,图中所示为PCB顶部的天线贴片,IC则位于天线PCB的背面。

半导体技术和封装

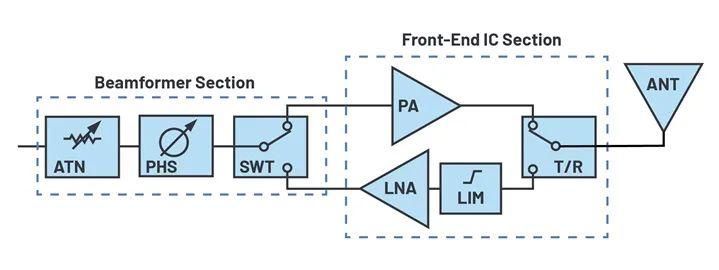

图3中显示了作为相控阵天线构建模块的微波和毫米波 (mmW) IC组件。在波束成型部分,衰减器调整每个天线元件的功率电平,以减少天线方向图中的栅瓣。移相器调整每个天线元件的相位以引导天线主波束,并且使用开关在发射器和接收器路径之间切换。在前端IC部分,使用功率放大器来发射信号,使用低噪声放大器来接收信号,最后,使用另一个开关在发射器和接收器之间进行切换。在过去的配置中,每个IC都作为独立的封装器件提供。更先进的解决方案使用集成单芯片单通道砷化镓 (GaAs) IC来实现这一功能。对于大部分阵列,在波束成型器之前都配有无源RF组合器网络、接收器/激励器和信号处理器,这一点图中未显示。

文章插图

图3. 相控阵天线的典型RF前端。

相控阵天线技术近年来的普及离不开半导体技术发展的推动。SiGe BiCMOS、绝缘体上硅 (SOI) 和体CMOS中的高级节点将数字和RF电路合并到一起。这些IC可以执行阵列中的数字任务,以及控制RF信号路径,以实现所需的相位和幅度调整。如今,我们已经可以实现多通道波束成型IC,此类IC可在4通道配置中调整增益和相位,最多可支持32个通道,可用于毫米波设计。在一些低功耗示例中,基于硅的IC有可能为上述所有功能提供单芯片解决方案。在高功率应用中,基于氮化镓的功率放大器显著提高了功率密度,可以安装到相控阵天线的单元构件中。这些放大器传统上一般使用基于行波管 (TWT) 的技术或基于相对低功耗的GaAs的IC。

- 芯片|功率半导体有多紧俏?博世亲自下场生产碳化硅芯片,目标产能上亿颗!

- 智能化|感知局限下,车路协同的“子弹”还得再飞会儿

- 路由器|千兆双频WiFi6,还能异地组网,什么神仙路由器只卖三百多?

- 酷比魔方|持续推进技术储备,网易星球区块链技术或成元宇宙入场券

- OPPO|OPPO未来科技大会正式官宣,官方明示将有旗舰新品和创新技术亮相

- 小米科技|雷军:小米12即将发布!首款搭载骁龙8手机,性能和功耗咋样?

- 亚马逊|麒麟990,麒麟980,麒麟985的机型现在还能入手嘛?

- 支付宝|突破2项关键技术,中科院又立功了,事关量子计算和3D打印

- 东芝|如何分辨手机配置的“好坏”?认清这四点,你也能成为行家

- 小米科技|华为手机想在2023年实现王者归来,只有2种可能,但可能性极低!