文章图片

自从 Lisa Su 博士让我们先睹为快地看了 Computex 2021 之后 , 围绕 AMD 新 3D V-Cache 技术的猜测就一直在波动 。 从那时起 , AMD和技术爱好者一直对新的小芯片堆叠方法可以产生实质性的性能提升 , 同时对延迟 , 响应能力和整体功能的影响最小 , 保持谨慎乐观 。 最近对带有V-Cache的EPYC处理器进行的测试提供了早期迹象 , 表明AMD的性能提升声明可能是正确的 。

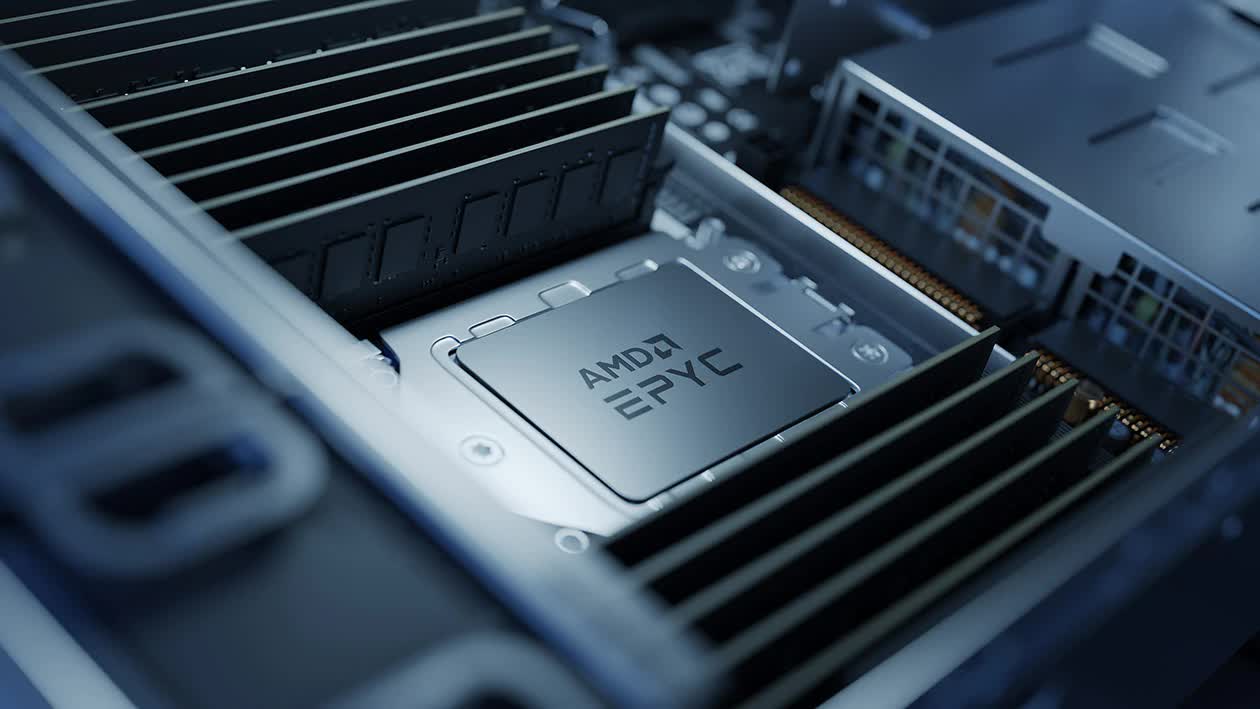

去年夏天 , 当AMD在Computex上宣布他们的时 , 没有人确切地知道会发生什么 。 虽然一些发烧友认为的大幅增加是一个令人兴奋的发展 , 但社区中的其他人发现自己对新产品无法大幅提高时钟速度 , 改善功耗等感到不安 。 上周五 , 科技新闻媒体Chips and Cheese公布了他们使用AMD新款Milan-X处理器之一的初始测试 , 该处理器带有3D V-Cache , 即面向服务器的EPYC 7V73X 。 到目前为止 , 事情看起来很有希望 。

【程序员|AMD 即将推出的 3D V-Cache 能够以最小的延迟增加来提高带宽】

根据该网站的摘要 , 与之前的米兰系列处理器(256MB)相比 , AMD已经设法大幅增加了处理器的缓存大小(768MB) 。 Chips and Cheese 的测试报告称 , 堆叠 CPU 和更大的 L3 缓存具有令人印象深刻的性能 , 而不会显著增加缓存和内存延迟 。 初始测试显示 , 延迟损失使增加保持在三到四个周期之间 。如果这些初步发现适用于AMD即将发布的AM4和AM5版本 , 例如那么芯片制造商无疑将继续探索与3D芯片堆叠相关的可能性和好处 。

AMD 目前的 3D 堆叠技术涉及将单个 V-Cache 小芯片绑定到处理器现有的核心复合芯片 (CCD) 和缓存 。 随着技术的成熟 , 未来的架构可能会使用额外的小芯片进一步扩展其L3缓存功能 。

我们将不得不拭目以待 , 看看未来会怎样 , 但如果基于EPYC的结果表明了什么是可能的 , 那么AMD可能会在下一轮CPU中提供另一个相当大的性能提升 。

- AMD|红米K50电竞版全部细节及参数

- 程序员|为什么程序员会有代码能跑就不要动的观点?是有毒吗?还是怎样?

- 程序员|在中国,有多少程序员干到46了?那么其他人去干什么了?

- 医生|医生真的比程序员好吗?有些真相说出来很扎心,有的让人想哭

- 软件|超级好用的办公软件,程序员新手快来收藏

- CPU|商用本处理器选AMD还是英特尔?10项实际应用测试大比拼

- 高通骁龙|年后哪款新品值得等?2022春季即将发布的新手机盘点

- 小米科技|2022年最佳显卡,AMD比NVIDIA性价比更高

- USB|苹果剑指中端市场,国内大厂再次出手,3000档水桶旗舰即将亮相

- 笔记本|AMD发力,Zen3+处理器6800H来了,独显本售6499元值得买吗