师从图灵奖得主,自研高端RISC-V芯片,对话睿思芯科创始人

文章插图

芯东西(公众号:aichip001)

作者 | 心缘

编辑 | 漠影

2020年黑天鹅事件接踵而至,但RISC-V创企睿思芯科并没受太多影响,相反,创始人谭章熹对这一年的进展很满意,芯片也在年底顺利量产。

距离RISC-V诞生已过去十年,这个每每被谈及,必与x86、Arm相提并论的新兴指令集架构,正在物联网、云端等更多场景中发挥潜能,并吸引了高通、英伟达、阿里巴巴、华为、三星、台积电等知名科技巨头及一众创企的积极布局。

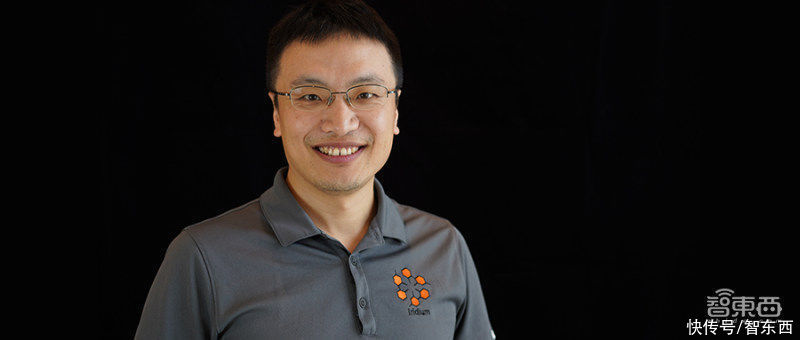

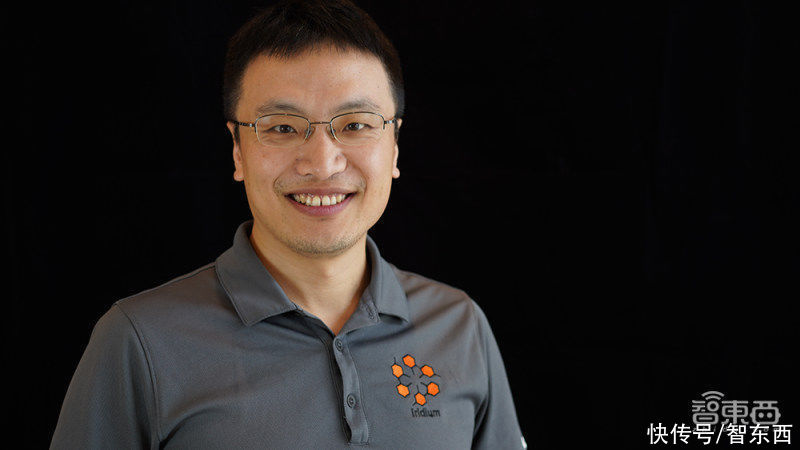

其中,睿思芯科是极具代表性的玩家之一,创始人谭章熹博士,是加州大学伯克利分校RISC-V原创项目组中的主力成员之一。他的博士生导师David A.Patterson教授是2017年图灵奖得主,也是精简指令集(RISC)的先驱。

文章插图

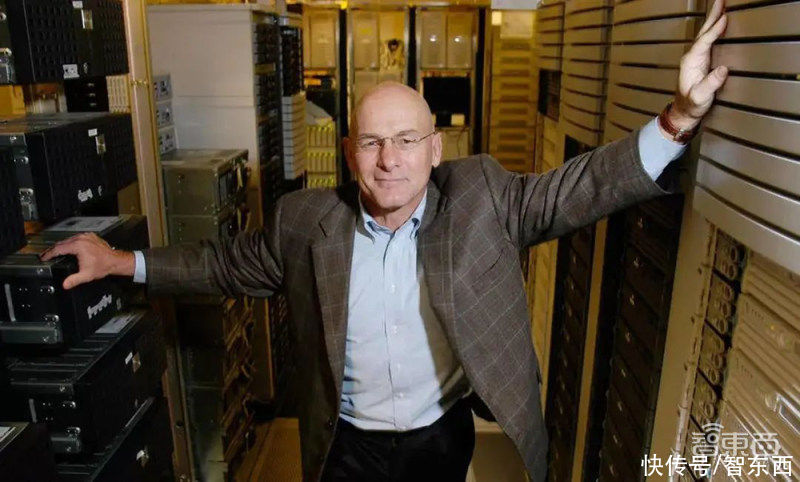

2017年图灵奖得主、计算机体系结构宗师David A.Patterson

“RISC-V是我看着长起来的。”谭章熹回忆说,当初因为研究遇到瓶颈,而x86、Arm有存在商业授权的问题,他所在的项目组决定创造一个全新的指令集架构,RISC-V由此诞生。

如今十年过去了,RISC-V从一个小众的实验室项目逐渐走到了产业中,通过各类电子产品开始进入千家万户。谭章熹也身兼数职,既作为创业者,也作为RISC-V国际协会的董事、RIOS Lab联合主任、清华-伯克利深圳研究院兼职教授,推动RISC-V的生态建设和人才培养。

文章插图

睿思芯科创始人兼CEO谭章熹

近日,芯东西与谭章熹进行了深入交流。除了讲述RISC-V从诞生至今的幕后故事外,谭章熹还分享了关于芯片研发落地的思考与经验,以及它有望带给半导体产业的独特价值。

一、从3个月暑期项目中诞生的全新指令集架构谭章熹本科就读于清华大学电子工程系,硕士就读于清华计算机系,随后赴加州大学伯克利分校攻读EECS博士,师从David A.Patterson教授。

读博期间,起初谭章熹和师弟做的是SPARC,但随着项目推进,他们发现SPARC的一些既定特征(例如register windows)束缚了他们的研究。

摆在眼前的路有两条,一是采用既有指令集,二是做一套新指令集。

指令集架构(ISA)犹如软件与硬件之间沟通的桥梁。如果将指令比作词汇,那么指令集架构就相当于汉语词典,一个程序相当于一本用汉语词典中的词汇写成的书,而指令集架构的所有者可以决定谁能用它的指令来构造硬件。

当时包括x86和Arm在内,所有指令集都无法满足他们的研发需求。x86已有上万条指令,Arm在2010年还没开发出64位,授权费用高昂、拿到授权时间长……种种束缚下,他们选择第二条路。

2010年5月,一个暑期项目正式启动,经过3个月的研发,全新指令集架构RISC-V新鲜出炉。

谭章熹的导师David A.Patterson是知名计算机体系结构宗师。早在四十年前,Patterson教授即开始带着研究生做第一代精简指令集(RISC)。第一、二、三、四代RISC都是在上世纪80年代实现,RISC-V直接沿用前四代的命名方法。

文章插图

在研发RISC-V时,项目组更加注重“精简”这一特性。比如x86有上万条指令,Arm有1000多条指令,而RISC-V的指令数只有40多条。

另外,RISC-V允许模块化扩展,将不同功能子集分的很细,不同模块之间可以自由排列组合,并支持可扩展定制指令。有能力的公司即可在指令集层面定制一个面向特定场景最优化的命令,来满足差异化运算需求,并有效降低硬件成本。

项目组将RISC-V放到网上后,慢慢有工程师认为UC伯克利发明的这个新指令集很好用。一开始,有人提问:“这个东西为什么不支持……?”项目组成员们还觉得好奇:“这是我们自己用来科研的,你凭什么给我提这些需求?”

项目组成员们觉得好奇:“这是我们自己用来科研的,你凭什么给我提这些需求?”

【师从图灵奖得主,自研高端RISC-V芯片,对话睿思芯科创始人】渐渐地,他们意识到RISC-V的影响力,决定把它变成开源项目,并于2015年成立RISC-V基金会,进一步推广RISC-V生态的发展。

二、RISC-V不是Arm的廉价替代,每一行代码都要由中国工程师敲出来RISC-V被业界寄予如此大的期望,与“开源”这个词密不可分。

一方面,它能降低架构授权门槛、节省芯片研发成本。企业或个人无需支付高额的架构授权费用,即可使用或修改RISC-V代码,实现芯片的定制优化。

- 付费|腾讯奖励员工21亿港元股票;爱奇艺被曝大规模裁员;抖音短剧开启付费模式;豆瓣被约谈,所有小组回复功能已暂停丨文娱周报

- 特斯拉|【黑马早报】爱奇艺回应大规模裁员;腾讯奖励员工20亿港元股票;蒙牛创始人牛根生彻底退出蒙牛;胡锡进呼吁联想高管降薪...

- 新东方在线|爱奇艺突然爆发最大规模裁员,每个部门都裁,部分团队全员被撤;传快手劝退低绩效员工,被疑变相裁员;腾讯斥资21亿奖励员工|雷峰早报

- 腾讯|QQ浏览器AI算法大赛颁奖典礼在深举办 发布全新技术品牌

- Java|DPReview公布年度摄影器材奖,尼康成赢家,苹果实力不俗

- 英特尔|?MIUI 13官方名单来了,小米:找到系统Bug,奖励手机一台

- 华为|最佳拍照手机出炉,华为并未获奖,第一名实在有点意外

- 一体机|一年斩获20项业界大奖!为何说TCL是中国电视的全球领跑者?

- 论文奖|连破17个云安全漏洞,中国青年学者获国际顶会CCS年度最佳论文奖

- 齐鲁在线网|黑芝麻智能华山二号A1000 Pro自动驾驶计算芯片再获两项大奖