嵌入式IEEE 1588精确时钟同步实现( 二 )

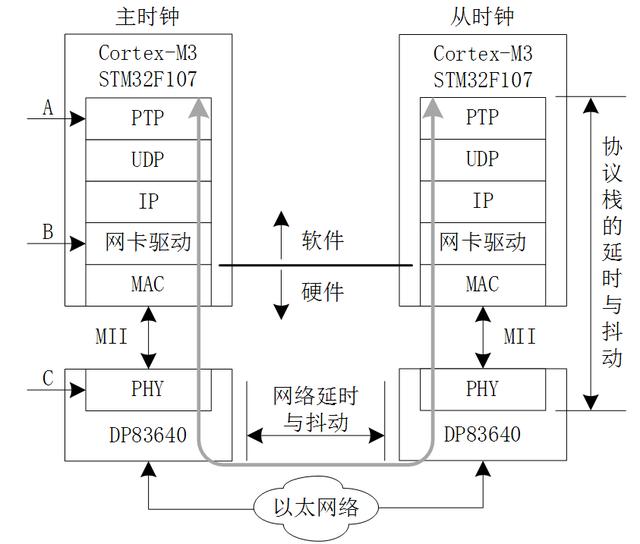

基于此 , 本实验时钟同步模块采用硬件标记时间戳的方式实现IEEE 1588协议 , 以GPS时钟为参考时钟源 , 并通过UDP/IP通信完成系统时钟同步 。 该时钟同步模块结构如图3所示 。

文章插图

文章插图

图3 时钟同步模块结构

时钟同步模块软件部分由驱动层、协议层、应用层组成 , 分别完成底层硬件控制、通信与同步、人机交互等功能 。

其中 , 驱动层分为标准驱动、以太网驱动以及PTP时钟驱动三部分;协议层分为TCP/IP协议与PTP协议两部分;应用层分为串口通信、以太网通信、实时时钟、精确时间同步等部分 。

在协议层中 , 嵌入式的TCP/IP协议栈采用LwIP实现 , LwIP协议栈以太网信息接收采取中断响应机制 , 当MAC接收到网络信号之后将引发以太网中断 , 主控芯片进入中断函数 , 先跳入相关底层处理函数 , 再进入协议栈做相应处理;而LwIP协议栈以太网信息发送则由应用层协议通过协议栈逐层向下传递信息 , 至MAC层后 , 调用相关底层处理函数进行发送 。

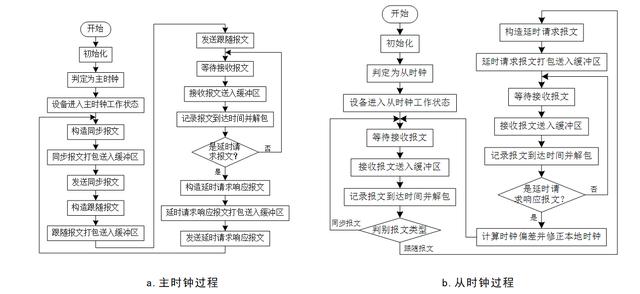

在PTP实现过程中 , 采用本地时钟算法 。 时钟同步系统上电后 , 各模块进入主从时钟判定程序 , 首先确定各模块的主、从时钟工作状态 , 进而通过UDP收发报文 , 记录各报文时间戳 , 计算主从时钟偏差修正本地时钟 。 图4软件系统流程图(a、b)中列出了主从时钟模块的同步工作过程 。

文章插图

文章插图

图4 软件系统流程图

同步性能测试与分析1 基于IEEE 1588时钟同步测试平台

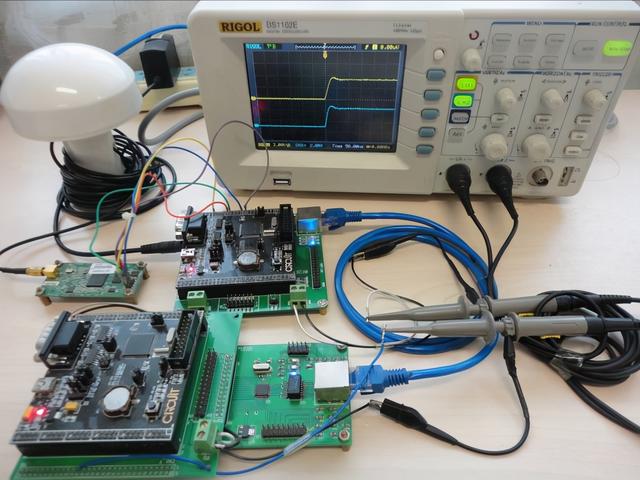

基于IEEE 1588时钟同步系统测试平台如图5所示 , 该系统工作在主从模式 , 采取点对点通信 , 精确时钟源由GPS授时模块提供 , 该时间作为PTP时钟源信号提供给IEEE 1588时钟同步模块 , 并将该模块时钟端口配置为主时钟状态 , 与之相对应的时钟模块配置为从时钟状态 。 在平台测试中 , 将两个时钟同步模块的PPS输出口接至数字示波器 , 来比较主从时钟节点的同步误差 , 测量该系统时钟同步精度 。

文章插图

文章插图

图5 基于IEEE 1588时钟同步测试平台

2 测试结果及分析

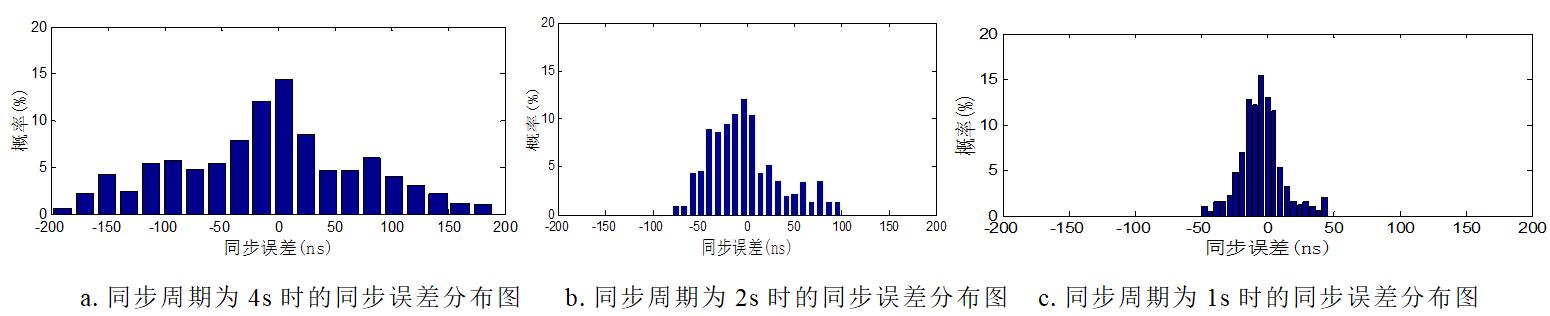

基于IEEE 1588时钟同步测试平台系统建立之后 , 需要对时钟同步系统的性能进行测试分析 。 本文根据同步报文发报周期取不同时间值(标准周期默认为2s) , 主要进行3次测试 , 实验同步报文发报周期分别取4s、2s、1s , 对主从时钟同步模块进行IEEE 1588时钟同步测试 。

文章插图

文章插图

图6 时钟同步测试结果

文章插图

文章插图

图7 测试结果对比图

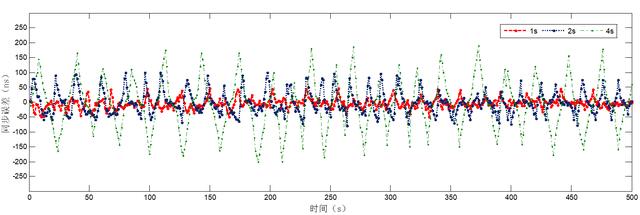

测试结果如图6所示 , 其中图中a、b、c分别为同步报文发报周期为4s、2s、1s时的同步误差分布图 , 图7为不同同步报文发送周期时的测试结果对比图 , 在此我们可以更直观的观测不同同步报文发送周期下的系统时钟同步误差 。

由图6、7测试结果表明:当同步报文发报周期取4s时 , 主从时钟节点之间IEEE 1588同步精度测试结果优于200ns;当同步报文发报周期取2s时 , 主从时钟节点之间IEEE 1588同步误差在100ns以内;当同步报文发报周期取1s时 , 主从时钟节点之间IEEE 1588同步精度能够达到50ns 。

文章插图

文章插图

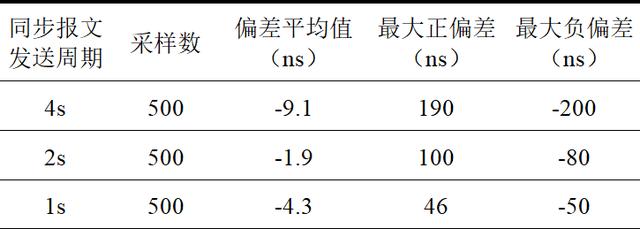

表1 不同同步报文发送周期下的时钟同步测试结果

表1中列出了同步报文不同发送周期下的时钟同步测试结果 , 同步报文发送周期越短 , 时钟同步精度越高 , 但随着同步报文发送周期的减小 , 系统内网络流量随之增加 , 在实际应用中网络负担也会随之加重 , 在运行中可能会降低系统时钟同步性能 。